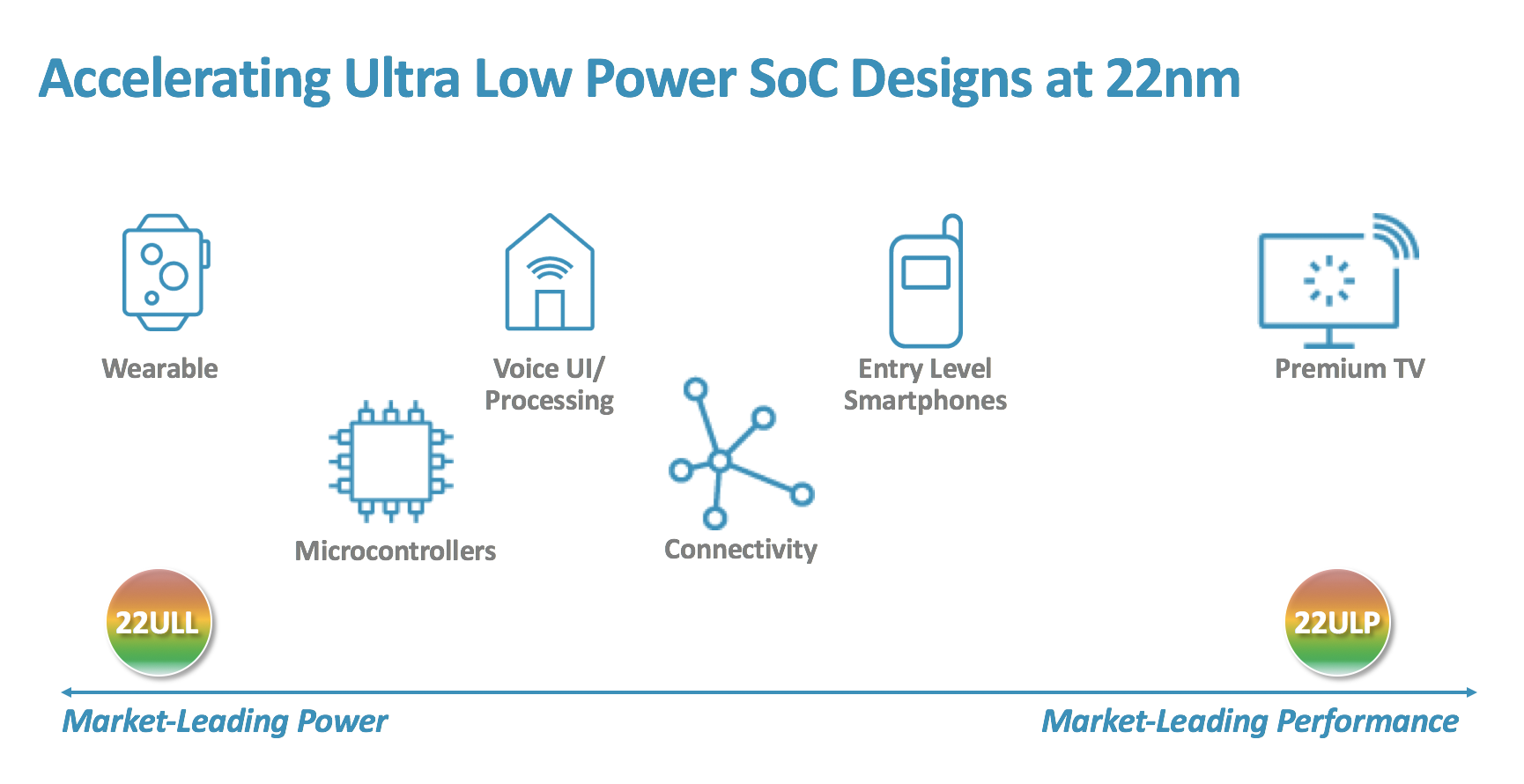

あなたのASIC設計は、可能な限り低リークで最小面積を必要としますか?FinFET技術を採用したいが、高価なウェハ・コストを懸念していますか?TSMCの22nmプロセスは、魅力的な選択肢を提供します。私たちは、28nm、40nm、およびそれ以上のプロセスを使用してきた多くのArmパートナーが、より低いリークとより小さな面積を達成するために22nmに移行し、所望の性能を維持、あるいは向上させているのを目の当たりにしています。

TSMCの22nm技術は、業界をリードするTSMCの28nmプロセスをベースに開発されたもので、その性能、消費電力、面積のスケーリングという点で、さまざまな市場セグメントで好まれているファウンドリ・ソリューションです。しかし、一部のIC設計者は、デジタルTV、セットアップ・ボックス、スマートフォン、コンシューマ製品などのアプリケーションにおいて、性能向上と低電源電圧の要件を満たす経済的な方法を探しています。そのようなIC設計にとって、TSMC 22nmは、28nmプロセスと比較して大幅な面積削減、速度向上、電力削減を実現し、コスト効率よく性能を向上させ、電力を削減する最良の方法です。

Armのパートナーの1つであるAmbiq Micro社は、ワイヤレス・コネクティビティとスマート・センシング技術の大手ライセンサーであり、Armと協力して40nmから22nmへのアップグレードを進めてきました。Ambiqは、Cortex-M、Crypto、CoreSight SoC-400、ETM、TSMC 22ULメモリ、TGOライブラリなどのArm IPを使用して、セキュリティを組み込んだサブスレッショルドリークを実現しました。Armソリューションの利点には、次のようなものがあります:

- UHVT/HVTデバイスを使用したULL-ULメモリ・コンパイラは、500MHzまでの性能を満たしながら、可能な限り低いリークを実現した。

- 6Vの周辺電圧をサポートすることで、IoTアプリケーションの電力削減に貢献した。

- 厚いゲート酸化膜(TGO)は、薄いゲート酸化膜と厚いゲート酸化膜の間で0.8Vから3.3Vの間でインターフェイスするように特別なレベルシフターが設計されているため、リークをさらに減少させた。

Ambiqのフィードバックに基づき、Arm Artisanメモリ・コンパイラは、競合IPと比較して面積を5%縮小し、リークを4%削減しながら、同じ性能基準を満たしています。

TSMCは、TSMC 22nm ULPおよびULLプロセス・テクノロジ向けのArtisanメモリ・コンパイラをサポートしています。これらのコンパイラは、低リークおよび低消費電力要件向けに最適化されています。Ambiqの最新の超低消費電力・高性能設計や、Armのソリューションがどのように役立つかについての詳細は、TSMCVirtual Technology SymposiumsおよびOIP Ecosystem ForumsのAmbiqおよびArmのオンラインサイト���ご覧ください。