# **PROGRAMMER'S GUIDE**

# Applicable to Apollo4 Family SoCs: Apollo4 SoC, Apollo4 Blue SoC, Apollo4 Plus SoC, Apollo4 Blue Plus SoC

Ultra-low Power Apollo SoC Family

Doc. ID: PG-A4-7p0

Doc. Revision: 7.0, October 2022

# **Legal Information and Disclaimers**

AMBIQ MICRO INTENDS FOR THE CONTENT CONTAINED IN THE DOCUMENT TO BE ACCURATE AND RELIABLE. THIS CONTENT MAY, HOWEVER, CONTAIN TECHNICAL INACCURACIES, TYPOGRAPHICAL ERRORS OR OTHER MISTAKES. AMBIQ MICRO MAY MAKE CORRECTIONS OR OTHER CHANGES TO THIS CONTENT AT ANY TIME. AMBIQ MICRO AND ITS SUPPLIERS RESERVE THE RIGHT TO MAKE CORRECTIONS, MODIFICATIONS, ENHANCEMENTS, IMPROVEMENTS AND OTHER CHANGES TO ITS PRODUCTS, PROGRAMS AND SERVICES AT ANY TIME OR TO DISCONTINUE ANY PRODUCTS, PROGRAMS, OR SERVICES WITHOUT NOTICE.

THE CONTENT IN THIS DOCUMENT IS PROVIDED "AS IS". AMBIQ MICRO AND ITS RESPECTIVE SUPPLIERS MAKE NO REPRESENTATIONS ABOUT THE SUITABILITY OF THIS CONTENT FOR ANY PURPOSE AND DISCLAIM ALL WARRANTIES AND CONDITIONS WITH REGARD TO THIS CONTENT, INCLUDING BUT NOT LIMITED TO, ALL IMPLIED WARRANTIES AND CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHT.

AMBIQ MICRO DOES NOT WARRANT OR REPRESENT THAT ANY LICENSE, EITHER EXPRESS OR IMPLIED, IS GRANTED UNDER ANY PATENT RIGHT, COPYRIGHT, MASK WORK RIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT OF AMBIQ MICRO COVERING OR RELATING TO THIS CONTENT OR ANY COMBINATION, MACHINE, OR PROCESS TO WHICH THIS CONTENT RELATE OR WITH WHICH THIS CONTENT MAY BE USED.

USE OF THE INFORMATION IN THIS DOCUMENT MAY REQUIRE A LICENSE FROM A THIRD PARTY UNDER THE PATENTS OR OTHER INTELLECTUAL PROPERTY OF THAT THIRD PARTY, OR A LICENSE FROM AMBIQ MICRO UNDER THE PATENTS OR OTHER INTELLECTUAL PROPERTY OF AMBIQ MICRO.

INFORMATION IN THIS DOCUMENT IS PROVIDED SOLELY TO ENABLE SYSTEM AND SOFTWARE IMPLE-MENTERS TO USE AMBIQ MICRO PRODUCTS. THERE ARE NO EXPRESS OR IMPLIED COPYRIGHT LICENSES GRANTED HEREUNDER TO DESIGN OR FABRICATE ANY INTEGRATED CIRCUITS OR INTE-GRATED CIRCUITS BASED ON THE INFORMATION IN THIS DOCUMENT. AMBIQ MICRO RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN. AMBIQ MICRO MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR DOES AMBIQ MICRO ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT, AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABIL-ITY, INCLUDING WITHOUT LIMITATION CONSEQUENTIAL OR INCIDENTAL DAMAGES. "TYPICAL" PARAME-TERS WHICH MAY BE PROVIDED IN AMBIQ MICRO DATA SHEETS AND/OR SPECIFICATIONS CAN AND DO VARY IN DIFFERENT APPLICATIONS AND ACTUAL PERFORMANCE MAY VARY OVER TIME. ALL OPERATING PARAMETERS, INCLUDING "TYPICALS" MUST BE VALIDATED FOR EACH CUSTOMER APPLICATION BY CUS-TOMER'S TECHNICAL EXPERTS. AMBIQ MICRO DOES NOT CONVEY ANY LICENSE UNDER NEITHER ITS PAT-ENT RIGHTS NOR THE RIGHTS OF OTHERS. AMBIQ MICRO PRODUCTS ARE NOT DESIGNED, INTENDED, OR AUTHORIZED FOR USE AS COMPONENTS IN SYSTEMS INTENDED FOR SURGICAL IMPLANT INTO THE BODY, OR OTHER APPLICATIONS INTENDED TO SUPPORT OR SUSTAIN LIFE, OR FOR ANY OTHER APPLICA-TION IN WHICH THE FAILURE OF THE AMBIQ MICRO PRODUCT COULD CREATE A SITUATION WHERE PER-SONAL INJURY OR DEATH MAY OCCUR. SHOULD BUYER PURCHASE OR USE AMBIQ MICRO PRODUCTS FOR ANY SUCH UNINTENDED OR UNAUTHORIZED APPLICATION, BUYER SHALL INDEMNIFY AND HOLD AMBIQ MICRO AND ITS OFFICERS, EMPLOYEES, SUBSIDIARIES, AFFILIATES, AND DISTRIBUTORS HARM-LESS AGAINST ALL CLAIMS, COSTS, DAMAGES, AND EXPENSES, AND REASONABLE ATTORNEY FEES ARIS-ING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PERSONAL INJURY OR DEATH ASSOCIATED WITH SUCH UNINTENDED OR UNAUTHORIZED USE, EVEN IF SUCH CLAIM ALLEGES THAT AMBIQ MICRO WAS NEGLIGENT REGARDING THE DESIGN OR MANUFACTURE OF THE PART.

# **Table of Content**

| 1. | Introduction                                                   | 12   |

|----|----------------------------------------------------------------|------|

| 2. | Document Revision History                                      | 13   |

| 3. | SoC Architecture                                               | 15   |

|    | 3.1 Interrupts                                                 | . 15 |

|    | 3.2 Memory Map                                                 |      |

|    | 3.3 Power Management Programming                               |      |

|    | 3.4 Instrumentation Trace Macrocell (ITM)                      |      |

|    | 3.5 SoC Control                                                |      |

|    | 3.6 Memory Controller Programming                              |      |

| 4. | Clock Generation (CLKGEN)                                      | 31   |

|    | 4.1 HFRC Auto-adjustment                                       |      |

|    | 4.2 Generating 100 Hz                                          |      |

|    | 4.3 Clock Enablement for Modules with a Special Mux            |      |

|    | 4.4 External 32.768 kHz Clock Input on X0                      |      |

| 5. | Real Time Clock (RTC)                                          | 39   |

|    | 5.1 Calendar Counters                                          |      |

|    | 5.2 Calendar Counter Reads                                     |      |

|    | 5.3 Alarms                                                     | . 39 |

|    | 5.4 Century Control and Leap Year Management                   |      |

|    | 5.5 Weekday Function                                           | . 40 |

| 6. | Counter/Timer Module (TIMER)                                   | 41   |

|    | 6.1 Counter/Timer Functions                                    |      |

|    | 6.2 Triggering Functions                                       | . 51 |

|    | 6.3 Clocking Timer/Counters with Other Counter/Timer Outputs   |      |

|    | 6.4 Global Timer/Counter Enable                                |      |

|    | 6.5 Generating the Sample Rate for the ADC                     | . 53 |

|    | 6.6 Generating the Sample Rate for the Audio ADC               | . 53 |

|    | 6.7 CLR and EN Details                                         | . 53 |

|    | 6.8 NOSYNC Function                                            | . 53 |

|    | 6.9 Counter Functions                                          | . 54 |

|    | 6.10 Interconnecting Timers                                    | . 54 |

| 7. | System Timer (STIMER)                                          | 55   |

|    | 7.1 Writing to the STIMER Compare Register on the Apollo4 Plus | . 55 |

| 8. | Watch Dog Timer (WDT)                                          | 56   |

|    | 8.1 Basic Operation                                            |      |

|    | 8.2 Register Functions                                         |      |

| 9. | General Purpose Input/Output (GPIO)                            | 57   |

|    | 9.1 General Purpose I/O (GPIO) Functions                       |      |

|    | 9.2 Pad Connection Summary                                     |      |

|    | 9.3 Module-specific Pad Configuration                          |      |

| 10. | General Purpose ADC and Temperature Sensor Module (GPADC)  | 83         |

|-----|------------------------------------------------------------|------------|

|     | 10.1 Clock Source and Divider                              |            |

|     | 10.2 Operating Modes and the Mode Controller               |            |

|     | 10.3 Interrupts                                            |            |

|     | 10.4 Generating the Sample Rate for the GPADC              |            |

|     |                                                            |            |

| 11. | Multi-bit Serial Peripheral Interface Master Module (MSPI) |            |

|     | 11.1 Configuration                                         |            |

|     | 11.2 PIO Operation                                         |            |

|     | 11.3 DMA Operations                                        |            |

|     | 11.4 Execute in Place (XIP) Operations                     |            |

|     | 11.5 Command Queueing (CQ)                                 |            |

|     | 11.6 Data Scrambling                                       |            |

|     | 11.7 Auto Power Down                                       |            |

|     | 11.0 Dourd/1 dokage Considerations for Mor 11 in Tilling   | 104        |

| 12. | I2C/SPI Master (IOM)                                       | 112        |

|     | 12.1 Programmer's Reference                                | 112        |

|     | 12.2 Interface Clock Generation                            | 112        |

|     | 12.3 Command Operation                                     | 113        |

|     | 12.4 FIFO                                                  | 114        |

|     | 12.5 I2C Interface                                         | 114        |

|     | 12.6 SPI Operations                                        |            |

|     | 12.7 Bit Orientation                                       |            |

|     | 12.8 SPI Flow Control                                      | 122        |

|     | 12.9 Minimizing Power                                      | 124        |

| 42  | 12C/SDI Slave /IOS)                                        | 405        |

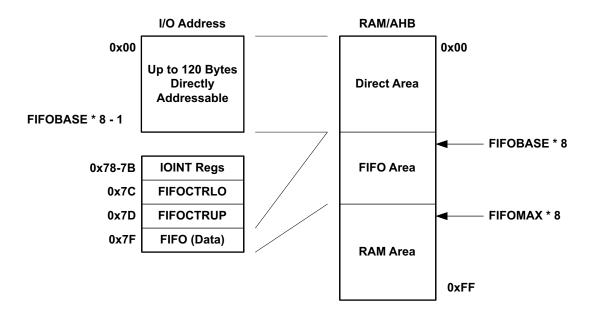

| 13. | 13.1 Local RAM Allocation                                  |            |

|     | 13.2 Direct Area Functions                                 |            |

|     |                                                            |            |

|     | 13.3 FIFO Area Functions                                   |            |

|     | 13.4 Rearranging the FIFO                                  |            |

|     | 13.5 Interface Interrupts                                  |            |

|     | 13.6 Command Completion Interrupts                         |            |

|     | 13.7 Host Address Space and Registers                      |            |

|     | 13.8 I2C Interface                                         |            |

|     |                                                            |            |

|     | 13.10 Bit Orientation                                      |            |

|     | 13.12 Host Side Address Space and Register                 |            |

|     | 13. 12 Flost Olde Address Opace and Negister               | 171        |

| 14. | Universal Asynchronous Receiver/Transmitter (UART)         | 146        |

|     | 14.1 Enabling and Selecting the UART Clock                 | 146        |

|     | 14.2 Configuration                                         | 146        |

|     | 14.3 Transmit FIFO and Receive FIFO                        |            |

| 4-  | Hairman Carial Bus (HCB)                                   | 4 4-       |

| 15. | Universal Serial Bus (USB)                                 |            |

|     | 15.1 Functional Overview                                   |            |

|     | 15.2 USB Reset                                             |            |

|     | 15.3 Soft Connect/Disconnect                               |            |

|     | 15.4 High-speed Mode                                       | 148<br>148 |

|     | LO O COO THELLUOL LIANUNUU                                 | 140        |

|               | 15.6 Index 0 Register Fields                                                                                                                                 |                   |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|               | 15.7 Response to USB Conditions or Host Actions                                                                                                              | 152               |

|               | 15.8 Suspend/Resume                                                                                                                                          | 153               |

|               | 15.9 Start of Frame Packets                                                                                                                                  | 154               |

|               | 15.10 Dynamic FIFO Sizing                                                                                                                                    | 155               |

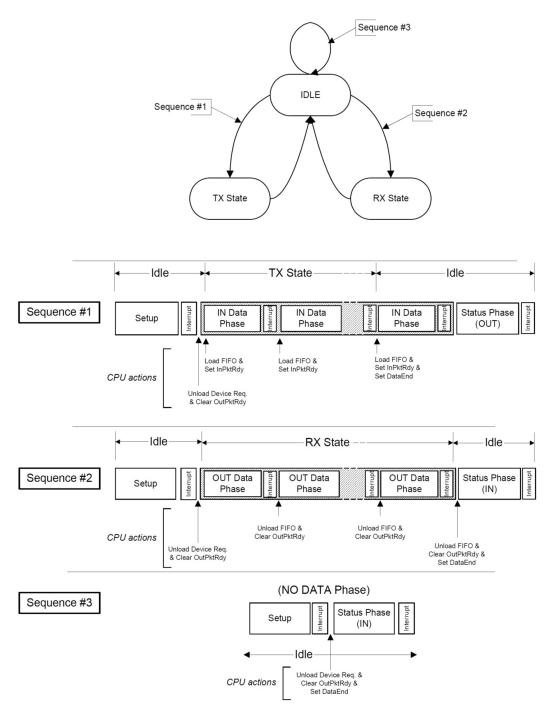

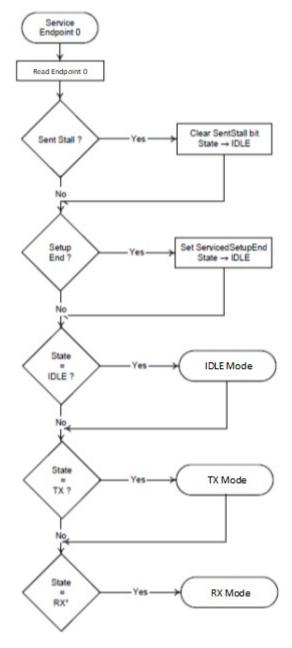

|               | 15.11 Endpoint 0 Handling                                                                                                                                    | 156               |

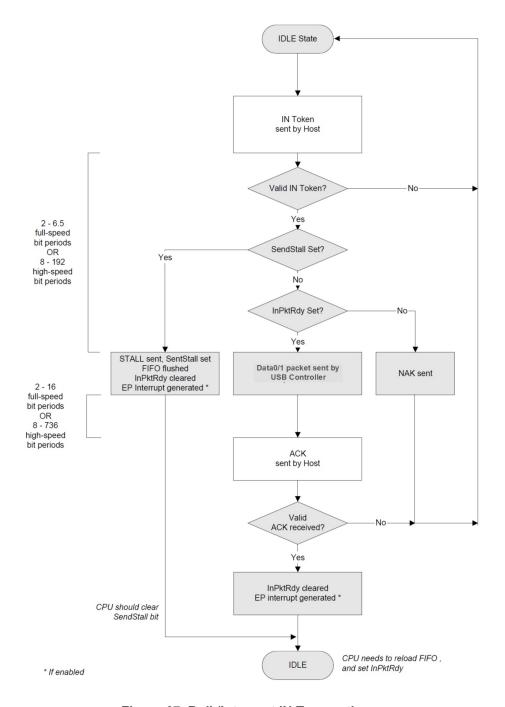

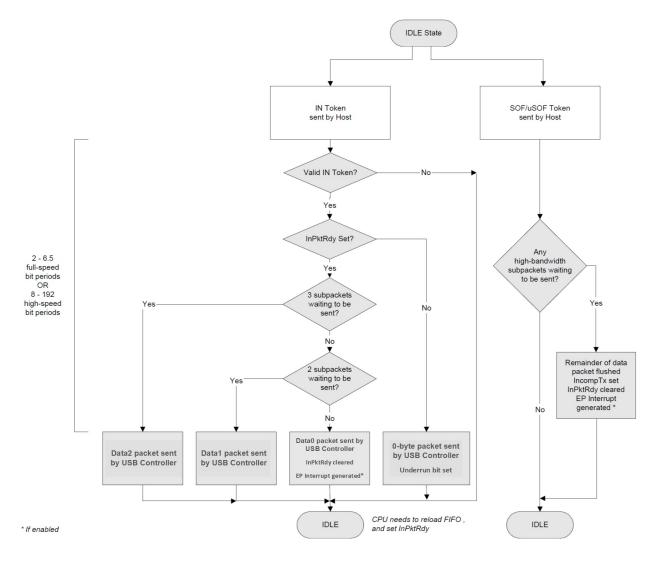

|               | 15.12 IN Endpoint Packet Handling                                                                                                                            | 167               |

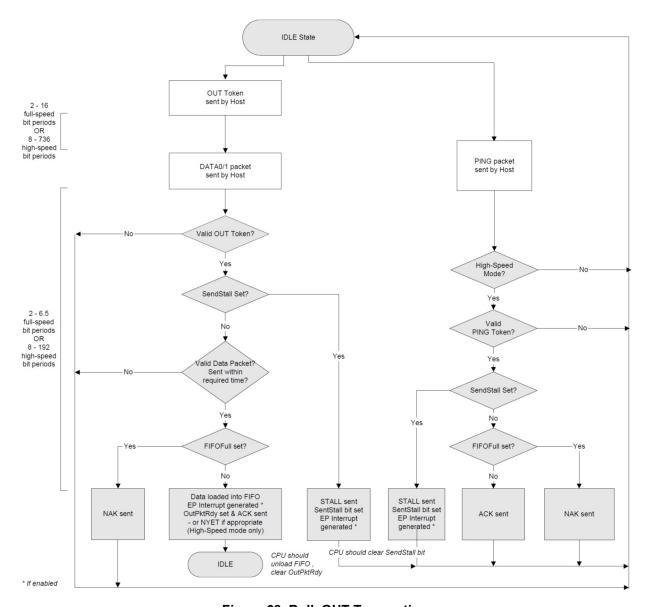

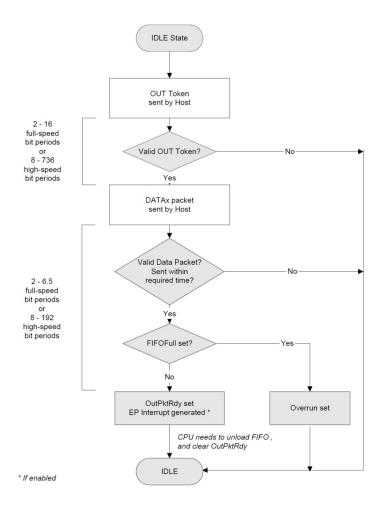

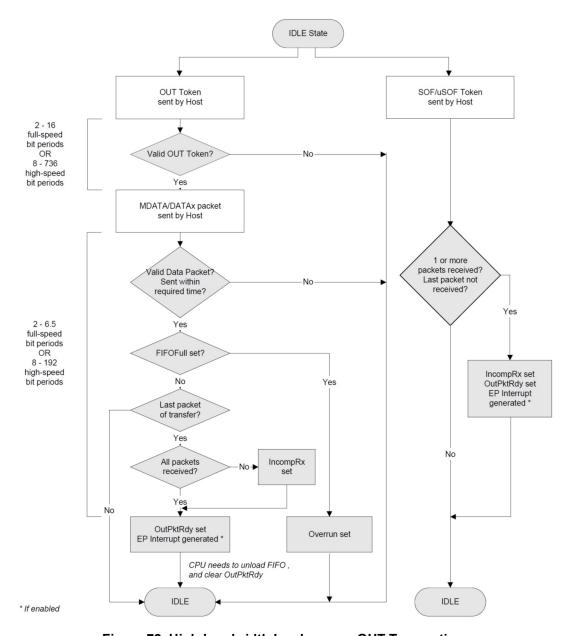

|               | 15.13 OUT Endpoint Packet Handling                                                                                                                           |                   |

|               | 15.14 Bulk Transactions                                                                                                                                      |                   |

|               | 15.15 Isochronous Transactions                                                                                                                               |                   |

|               | 15.16 Transaction Flows                                                                                                                                      |                   |

|               | 15.17 Test Modes                                                                                                                                             |                   |

| 16 (          | Secure Digital Input Output (SDIO)                                                                                                                           | 200               |

| 10.           | Secure Digital Input Output (SDIO)                                                                                                                           |                   |

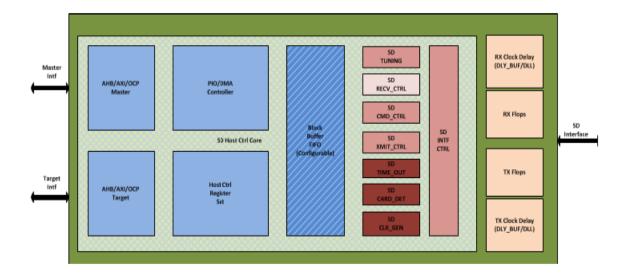

|               | 16.1 Functional Description                                                                                                                                  |                   |

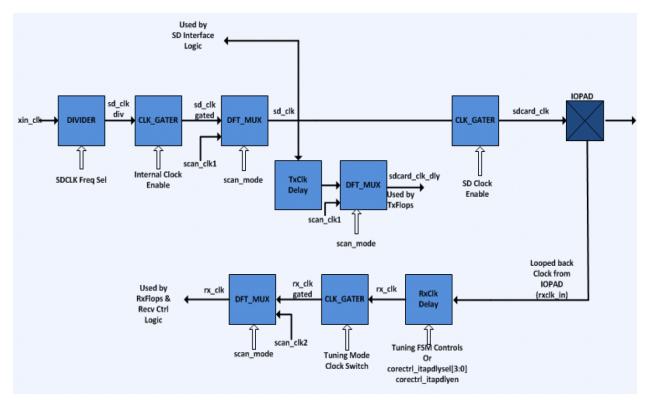

|               | 16.2 Clocks                                                                                                                                                  |                   |

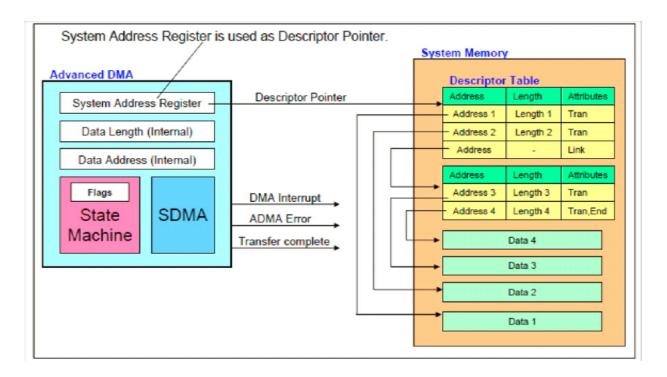

|               | 16.3 Advanced DMA                                                                                                                                            |                   |

|               | 16.4 Driver flow sequence                                                                                                                                    |                   |

|               | 16.5 Using the AmbiqSuite SDK to Program and Use the SDIO Module                                                                                             | 215               |

| 17. I         | Display Controller (DC)                                                                                                                                      | 220               |

|               | 17.1 Software Support                                                                                                                                        |                   |

|               | 17.2 Timing Generator                                                                                                                                        |                   |

|               | 17.3 Layer Overlays                                                                                                                                          |                   |

|               | 17.4 Blending Modes                                                                                                                                          |                   |

|               | 17.5 Palette/Gamma Correction                                                                                                                                |                   |

|               |                                                                                                                                                              |                   |

|               | 17.6 Dithering                                                                                                                                               |                   |

|               | 17.7 Color Modes                                                                                                                                             |                   |

|               | 17.8 TSc Framebuffer Decompression                                                                                                                           |                   |

|               | 17.9 Display Formats                                                                                                                                         | 235               |

| 18. I         | Display Serial Interface (DSI)                                                                                                                               | 248               |

| 10 /          | Graphics and the GEV Library on the Apollo4 Family MCIIs                                                                                                     | 240               |

| 13. \         | Graphics and the GFX Library on the Apollo4 Family MCUs                                                                                                      |                   |

|               | 19.1 Introduction to Graphics                                                                                                                                |                   |

|               | 19.2 GPU and Graphics Software Support                                                                                                                       |                   |

|               | 19.3 GFX Library Architecture                                                                                                                                |                   |

|               | 19.4 Graphics Pipeline of the GPU                                                                                                                            |                   |

|               | 19.5 Frame Buffer Compression                                                                                                                                |                   |

|               | 19.6 GFX Library API Guidelines                                                                                                                              |                   |

|               | 19.7 Color Modes and Binding Textures                                                                                                                        |                   |

|               | 19.8 Geometry Primitives                                                                                                                                     | 277               |

|               | 40 0 DL                                                                                                                                                      |                   |

|               | 19.9 Blending                                                                                                                                                | 278               |

|               | 19.9 Blending                                                                                                                                                |                   |

|               | 19.10 Fonts                                                                                                                                                  | 285               |

|               |                                                                                                                                                              | 285<br>287        |

| 20.           | 19.10 Fonts                                                                                                                                                  | 285<br>287<br>298 |

| <b>20</b> . l | 19.10 Fonts                                                                                                                                                  |                   |

| <b>20</b> . l | 19.10 Fonts  19.11 GFX Library Platform Porting  19.12 GFX Library Functions  PDM-to-PCM Converter (PDM)  20.1 PDM Clock Configuration                       |                   |

| <b>20</b> . l | 19.10 Fonts  19.11 GFX Library Platform Porting  19.12 GFX Library Functions  PDM-to-PCM Converter (PDM)  20.1 PDM Clock Configuration  20.2 Operating Modes |                   |

| <b>20</b> . l | 19.10 Fonts  19.11 GFX Library Platform Porting  19.12 GFX Library Functions  PDM-to-PCM Converter (PDM)  20.1 PDM Clock Configuration                       |                   |

|       | 20.5 Low Pass Filter (LPF)                        | 366 |

|-------|---------------------------------------------------|-----|

|       | 20.6 High Pass Filter (HPF)                       |     |

| 21. L | Low Power Analog Audio Interface                  | 368 |

|       | 21.1 Automatic Sample Accumulation and Scaling    |     |

|       | 21.2 Sixteen Entry Result FIFO                    |     |

|       | 21.3 DMA                                          |     |

|       | 21.4 Window Comparator                            |     |

|       | 21.5 Operating Modes and the Mode Controller      | 373 |

|       | 21.6 Interrupts                                   |     |

|       | 21.7 Generating the Sample Rate for the Audio ADC | 377 |

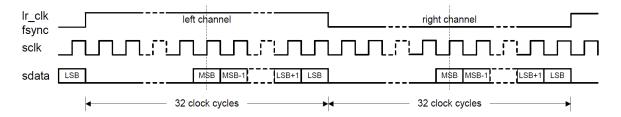

| 22. I | Inter-IC Sound (I2S)                              | 378 |

|       | 22.1 I2S Clock Management                         |     |

|       | 22.2 DMA                                          |     |

|       | 22.3 Interrupts                                   | 380 |

|       | 22.4 Data Configurations                          | 380 |

|       | 22.5 Configuration and Control                    |     |

|       | 22.6 Serial Audio Interface                       |     |

| 23. ( | Ordering Information                              | 388 |

# **List of Figures**

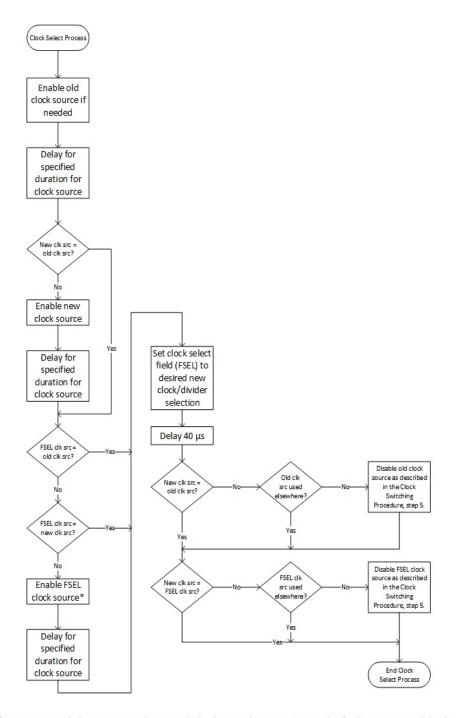

|             | Clock Source Selection Flowchart                              |       |

|-------------|---------------------------------------------------------------|-------|

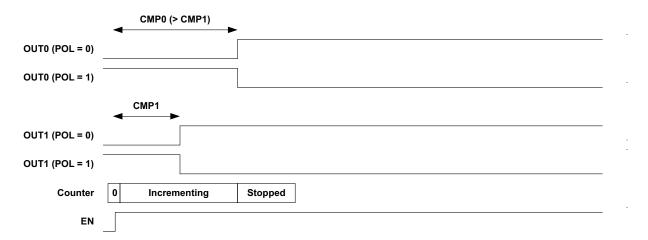

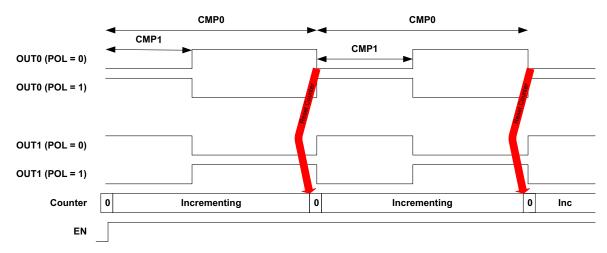

| Figure 2. 7 | Fimer Edge Mode (TMRnFN = 0x1) - CMP0 > CMP1                  | . 44  |

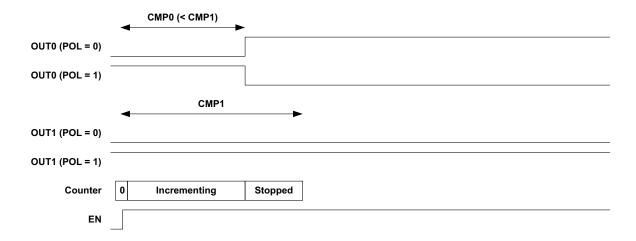

|             | Fimer Edge Mode (TMRnFN = 0x1) - CMP0 < CMP1                  |       |

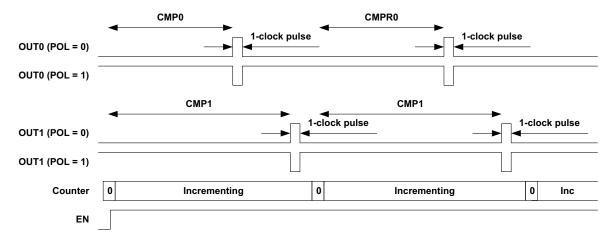

| Figure 4. 7 | Fimer Repeated Pulse Up-counter Compare Mode (TMRnFN = 0x2)   | . 46  |

|             | Fimer PWM Mode (TMRnFN = 0x4)                                 |       |

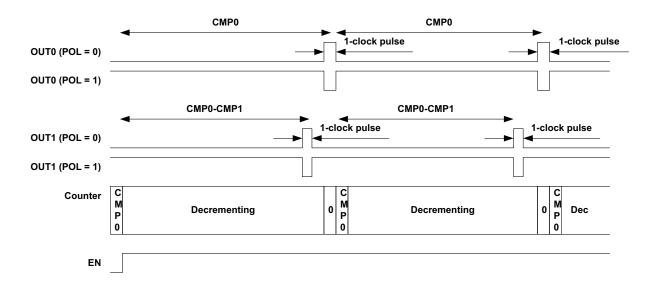

| Figure 6. 7 | Fimer Repeated Pulse Down-counter Compare Mode (TMRnFN = 0x6) | . 48  |

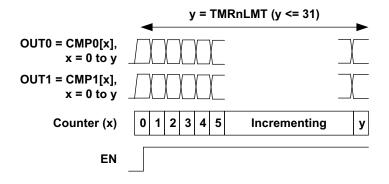

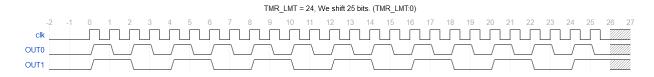

|             | Fimer Single 32-bit Pattern Output (TMRnFN = 0xC)             |       |

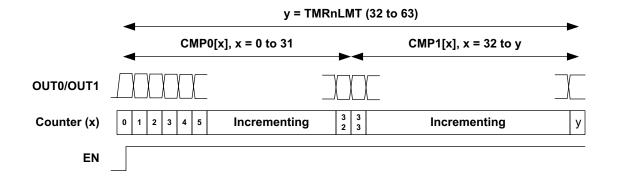

| Figure 8. 7 | Fimer Single 64-bit Pattern Output (TMRnFN = 0xC)             | . 49  |

|             | Single 32-bit Pattern Output                                  |       |

| Figure 10.  | Single 64-bit Pattern Output                                  | . 50  |

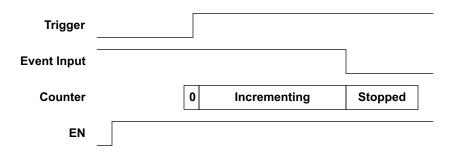

| Figure 11.  | Timer Event Counter (TMRnFN = 0xE)                            | . 51  |

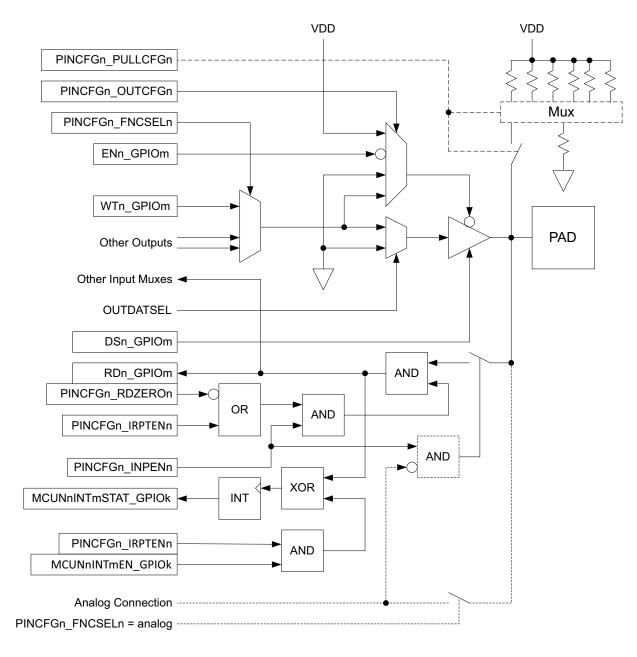

| Figure 12.  | Pad Connection Details                                        | . 60  |

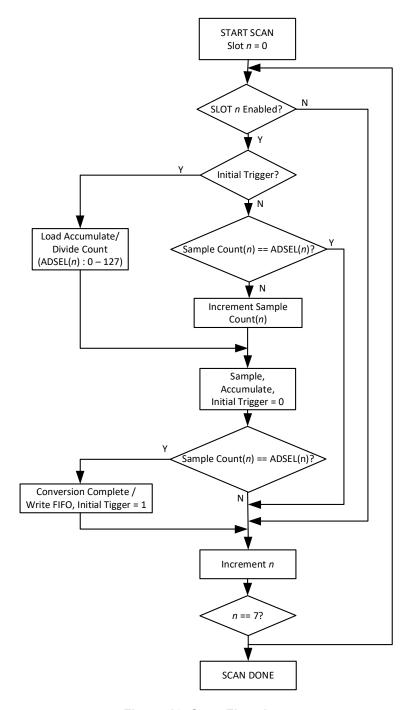

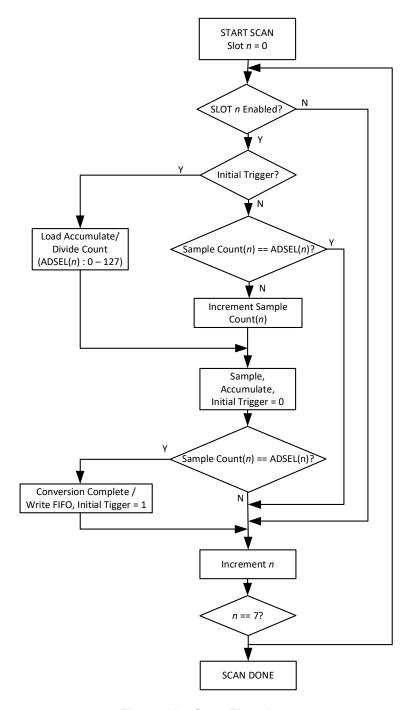

| Figure 13.  | Scan Flowchart                                                | . 91  |

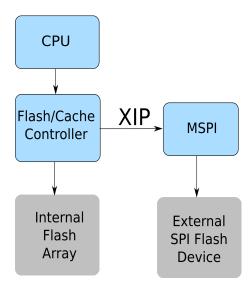

| Figure 14.  | XIP Block Diagram                                             | . 98  |

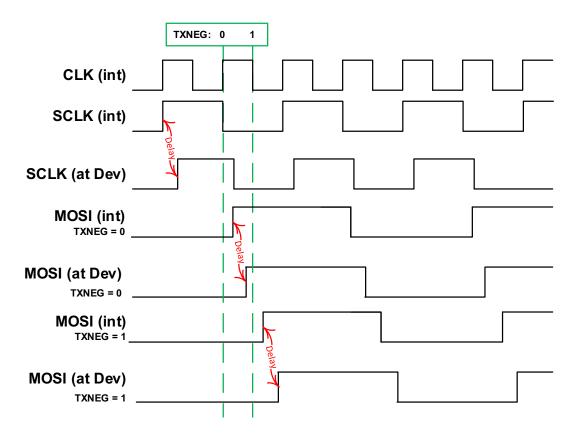

| Figure 15.  | MSPI TX Interface Timing at SCLK = 48 MHz                     | 105   |

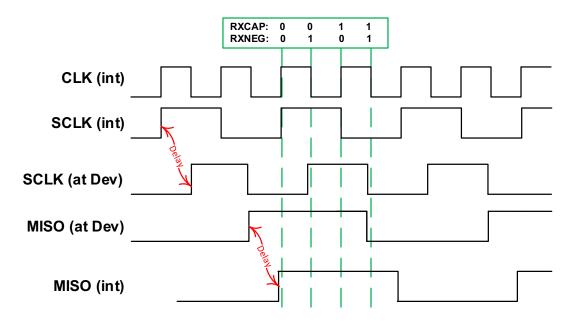

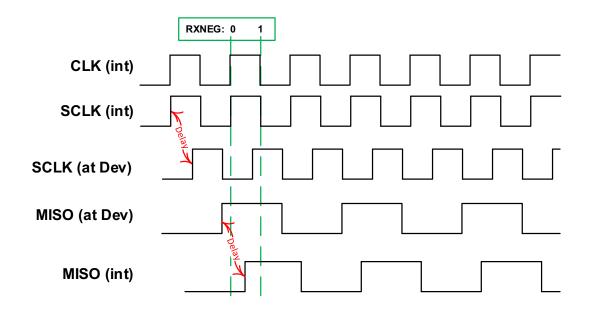

|             | MSPI RX Interface Timing at SCLK = 48 MHz                     |       |

|             | MSPI RX Interface Timing at SCLK = 96 MHz                     |       |

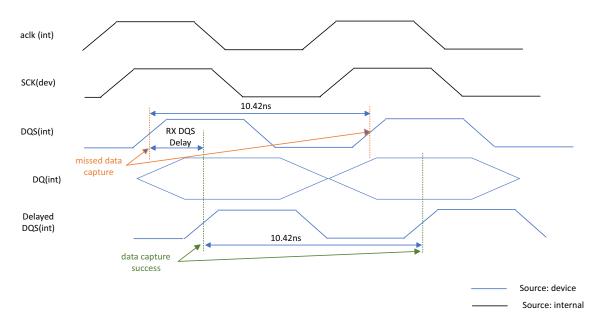

|             | RX DQS Delay in SDR DQS Mode (96MHz)                          |       |

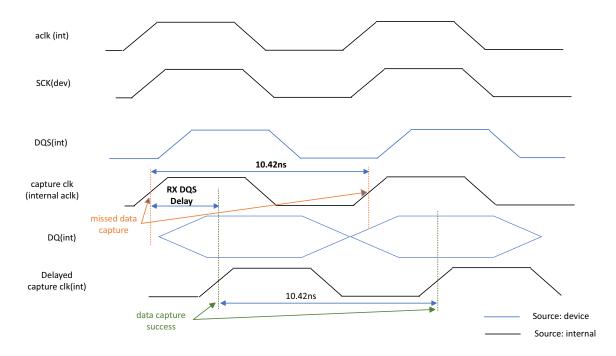

|             | RX DQS Delay in SDR Non-DQS Mode (96MHz)                      |       |

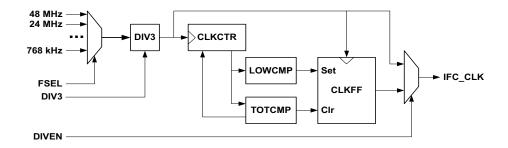

|             | I2C/SPI Master Clock Generation                               |       |

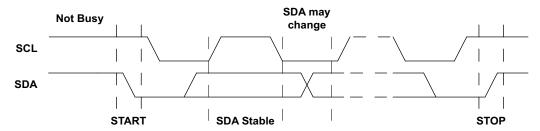

|             | Basic I2C Conditions                                          |       |

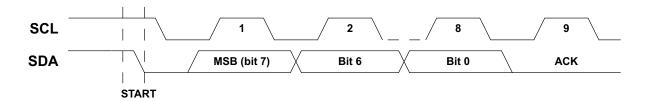

| •           | I2C Acknowledge                                               |       |

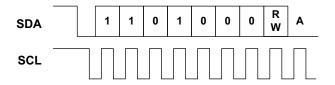

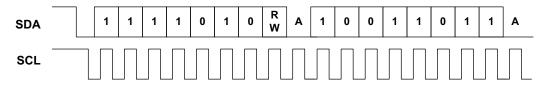

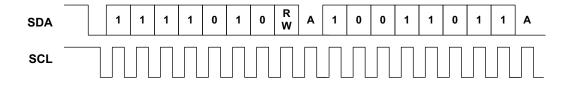

|             | I2C 7-bit Address Operation                                   |       |

|             | I2C 10-bit Address Operation                                  |       |

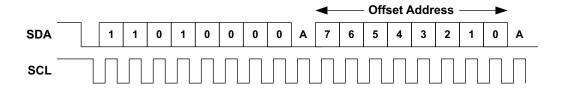

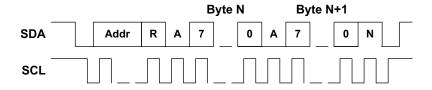

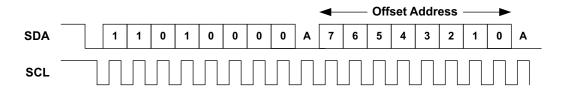

|             | I2C Offset Address Transmission                               |       |

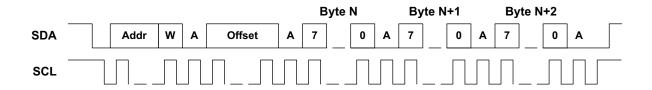

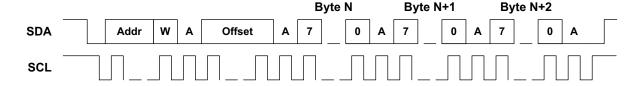

|             | I2C Write Operation with Address Offset                       |       |

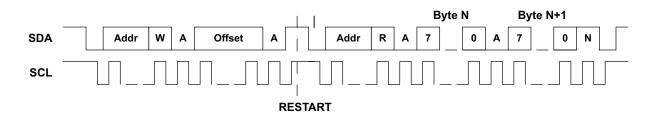

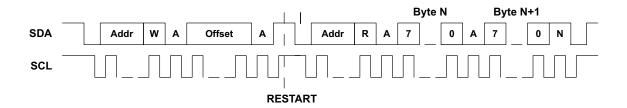

|             | I2C Read Operation with Address Offset                        |       |

|             | I2C Write Operation with No Address Offset                    |       |

|             | I2C Read Operation with No Address Offset                     |       |

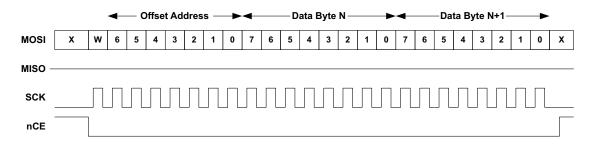

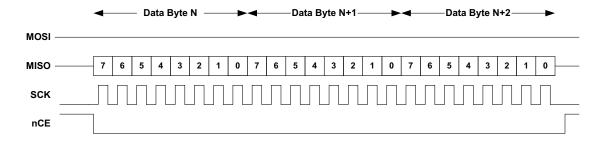

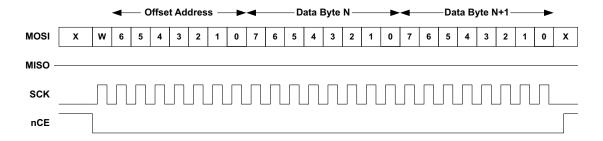

| •           | SPI Normal Write Operation (Single-byte Offset Address)       |       |

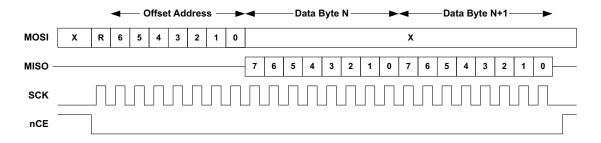

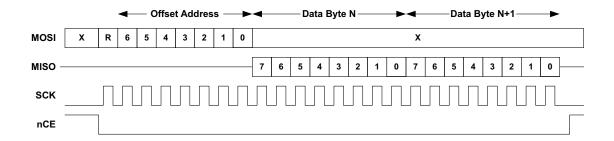

|             | SPI Normal Read Operation                                     |       |

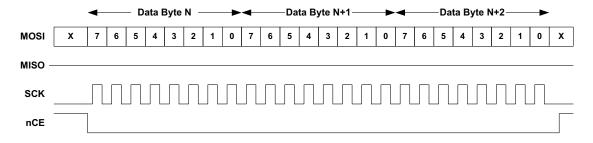

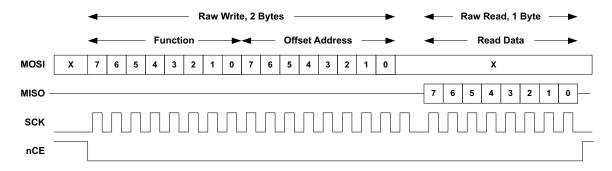

|             | SPI Raw Write Operation                                       |       |

|             | SPI Raw Read Operation                                        |       |

|             | SPI Combined Operation                                        |       |

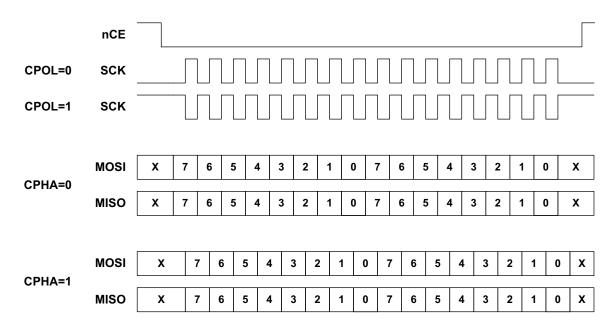

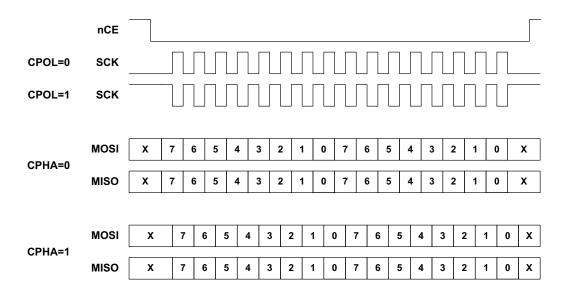

| •           | SPI CPOL and CPHA                                             |       |

| •           | Flow Control at Beginning of a Write Transfer                 |       |

|             | Flow Control at Beginning of a Raw Read Transfer              |       |

|             |                                                               | 124   |

| 9           | Flow Control in the Middle of a Read Transfer                 | . – . |

|             | I2C/SPI Slave Module LRAM Addressing in Standard Address Mode |       |

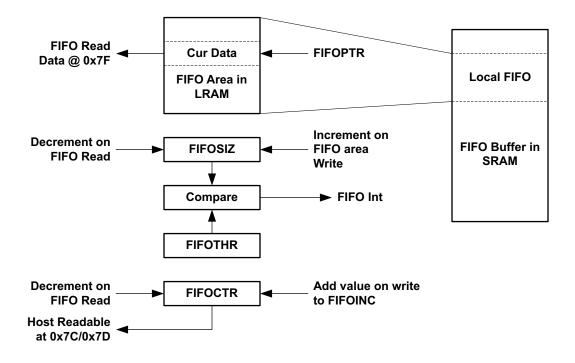

|             | I2C/SPI Slave Module FIFO                                     |       |

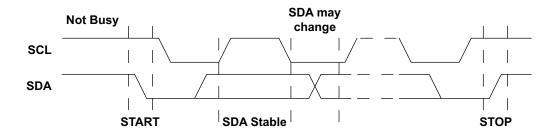

|             | Basic I2C Conditions                                          |       |

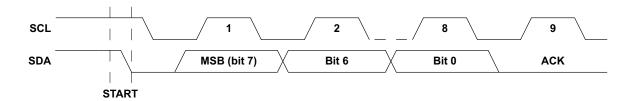

| •           | I2C Acknowledge                                               |       |

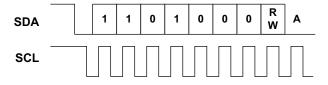

|             | I2C 7-bit Address Operation                                   |       |

| -           | I2C 10-bit Address Operation                                  |       |

|             | I2C Offset Address Transmission                               |       |

| •           | I2C Write Operation                                           |       |

| •           | I2C Read Operation                                            |       |

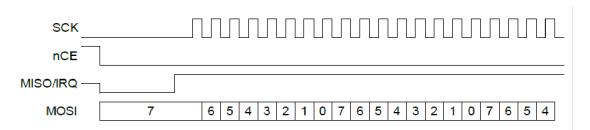

| •           | SPI Write Operation                                           |       |

| •           | SPI Read Operation                                            |       |

|             | SPI CPOL and CPHA                                             |       |

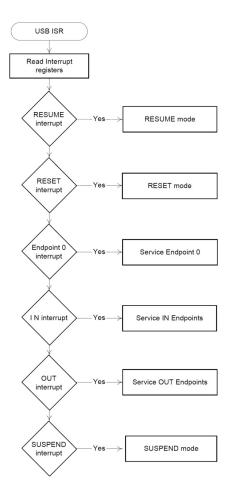

|             | USB Interrupt Service Routine                                 |       |

|             | upt eer nee i teamie                                          |       |

|            | Endpoint 0 States                                                             |     |

|------------|-------------------------------------------------------------------------------|-----|

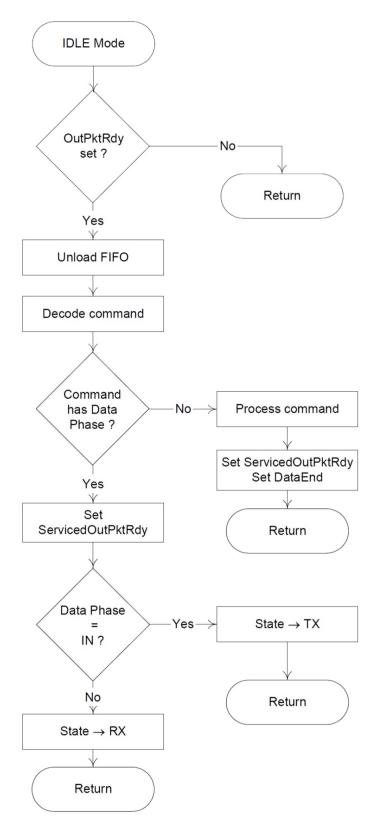

|            | Endpoint 0 Service Routine                                                    |     |

|            | SETUP Phase of Control Transfer                                               |     |

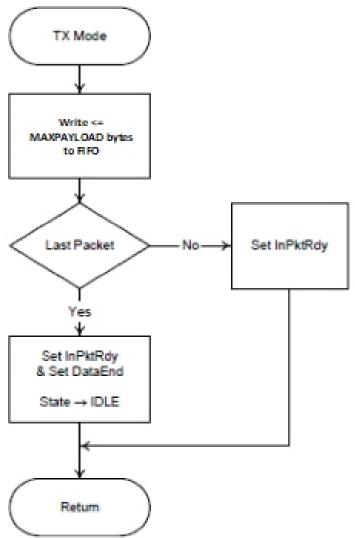

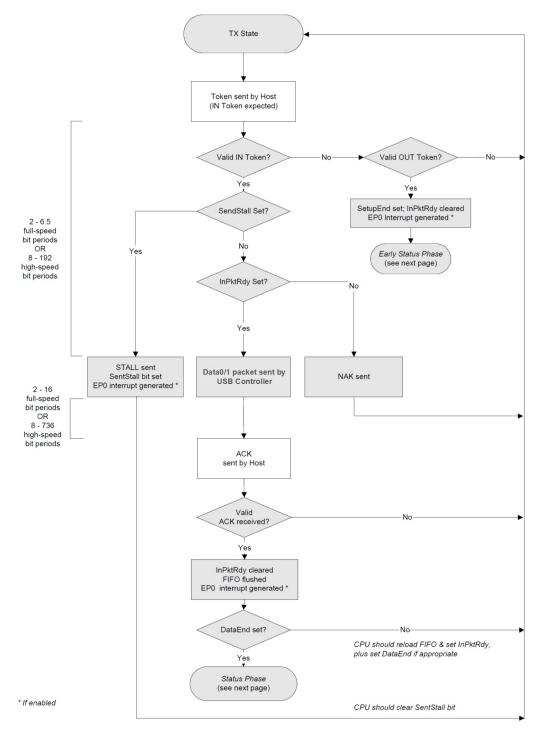

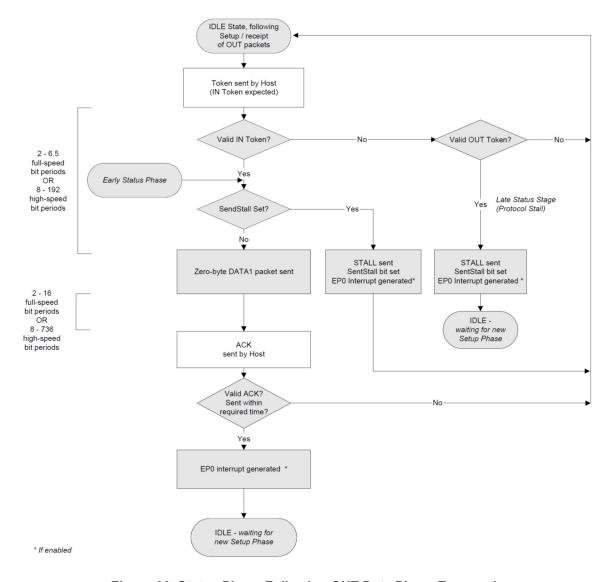

|            | IN Data Phase for Control Transfer                                            |     |

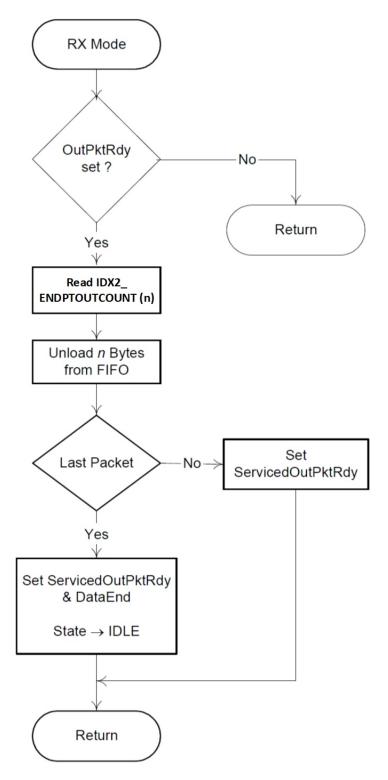

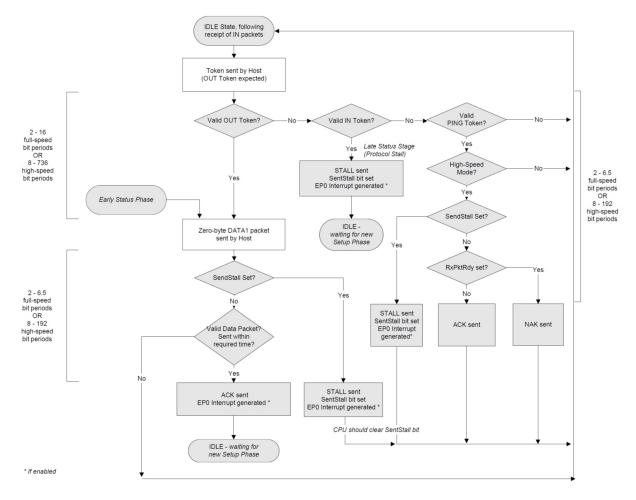

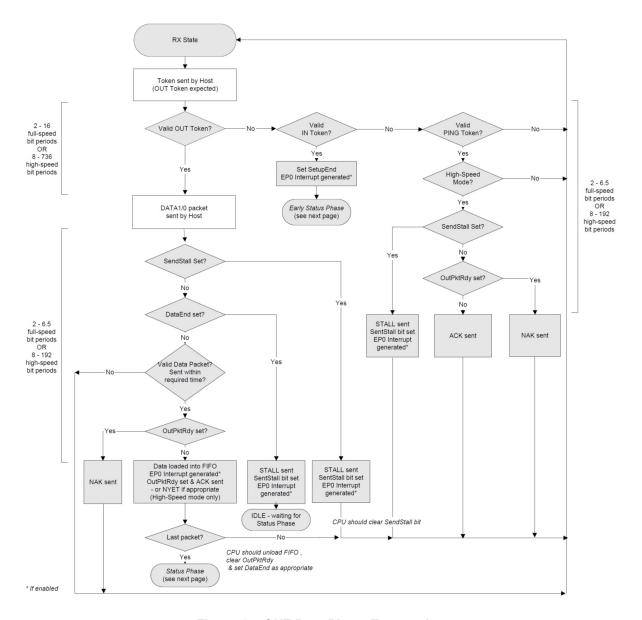

|            | OUT Data Phase for Control Transfer                                           |     |

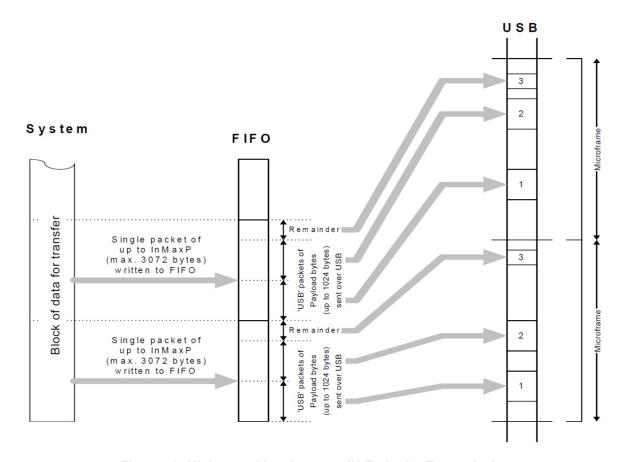

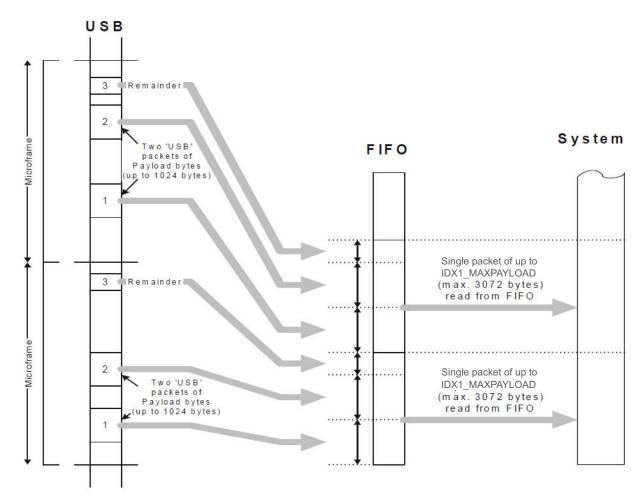

| Figure 58. | High-speed Isochronous IN Endpoint Transmission                               | 169 |

|            | Packets Sent per Microframe                                                   |     |

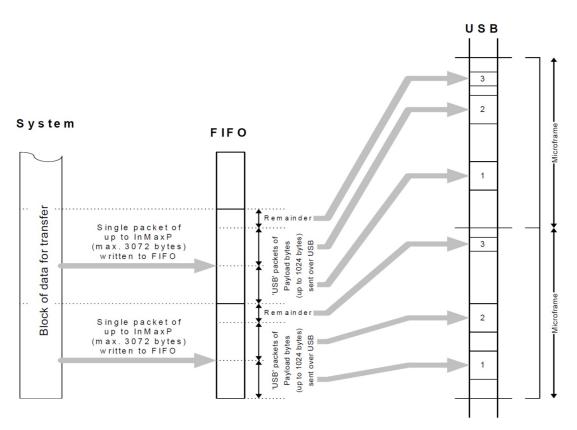

| Figure 60. | High-Speed High-Bandwidth IN Endpoint                                         | 185 |

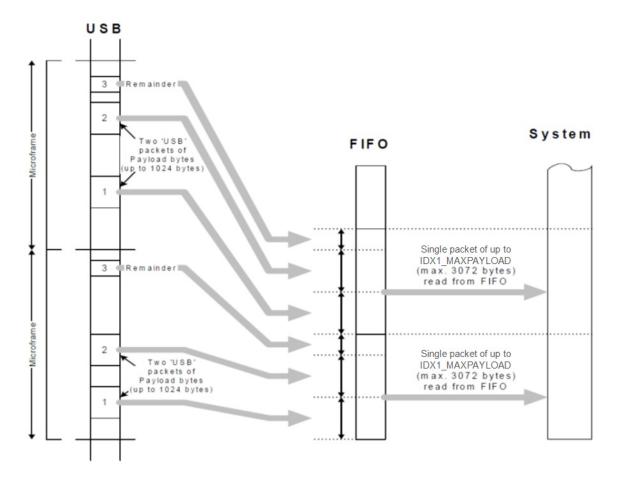

|            | High-speed High-bandwidth OUT Endpoint                                        |     |

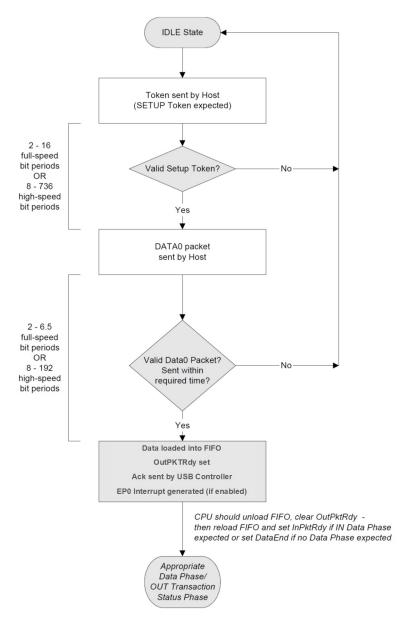

| Figure 62. | Setup Phase Transaction                                                       | 188 |

| Figure 63. | IN Data Phase Transaction                                                     | 189 |

| Figure 64. | Status Phase Following IN Data Phase Transaction                              | 190 |

|            | OUT Data Phase Transaction                                                    |     |

| Figure 66. | Status Phase Following OUT Data Phase Transaction                             | 192 |

|            | Bulk/Interrupt IN Transaction                                                 |     |

| Figure 68. | Bulk OUT Transaction                                                          | 194 |

| Figure 69. | Full-speed Isochronous IN Transaction                                         | 195 |

| Figure 70. | Full-speed Isochronous OUT Transaction                                        | 196 |

|            | High-bandwidth Isochronous IN Transaction                                     |     |

|            | High-bandwidth Isochronous OUT Transaction                                    |     |

|            | SD/SDIO Host Controller Interface Block Diagram                               |     |

| _          | SDIO Module Clock Derivation                                                  |     |

| _          | ADMA2 Block Diagram                                                           |     |

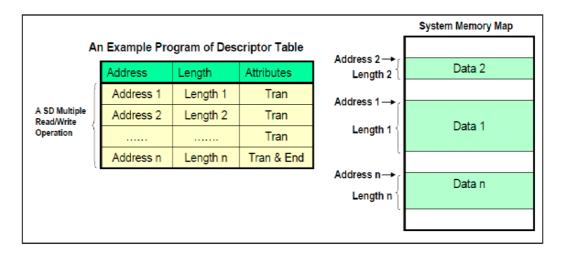

| _          | Example Descriptor Table                                                      |     |

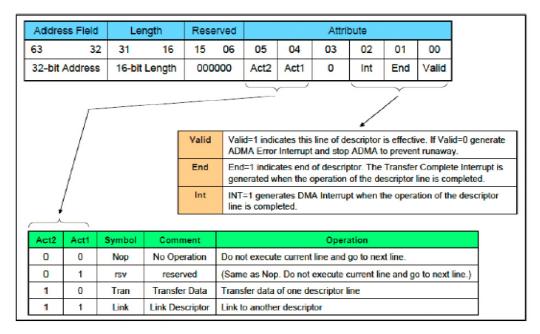

|            | 32-bit Addressing Descriptor Table                                            |     |

| _          | Descriptor Table Length Field Definitions                                     |     |

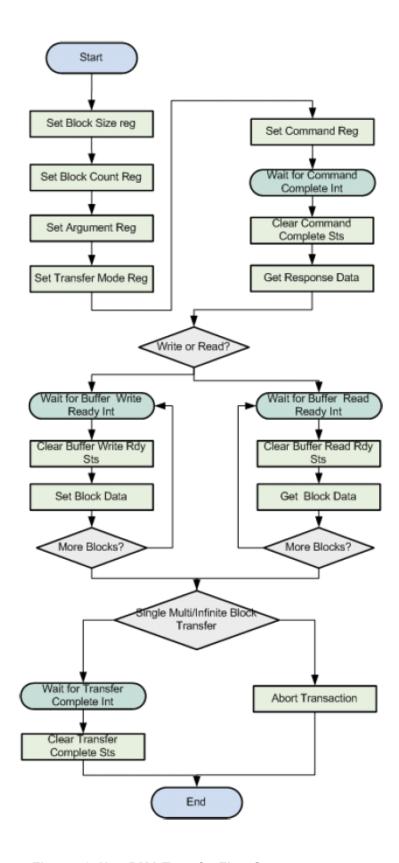

|            | Non-DMA Transfer Flow Sequence                                                |     |

| _          | DMA Transfer Flow Sequence                                                    |     |

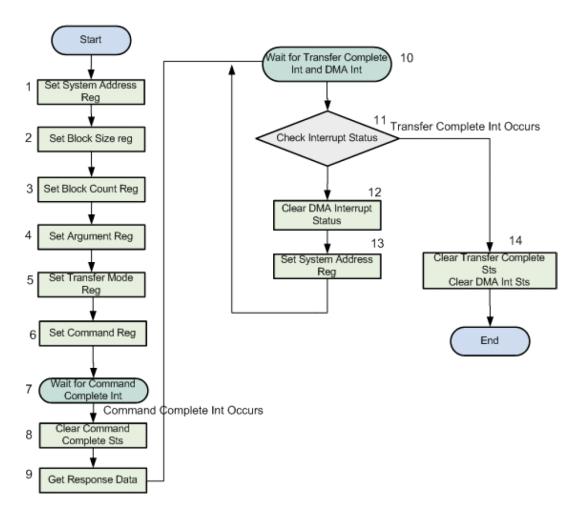

| _          | ADMA Transaction Flow Sequence                                                |     |

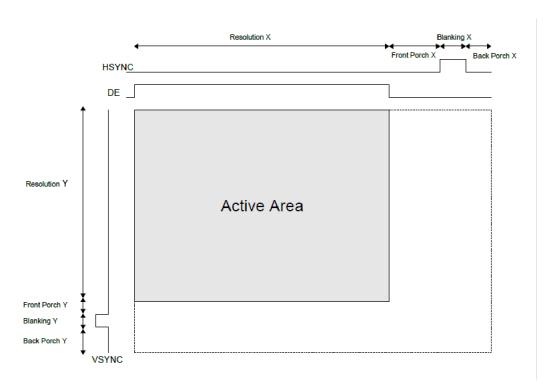

| _          | Display Controller Video Timing                                               |     |

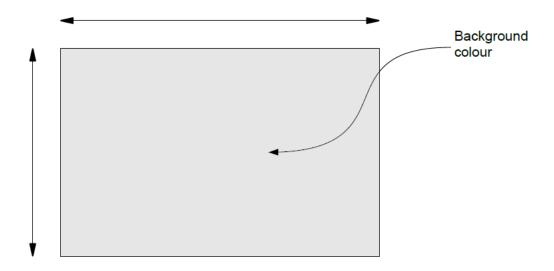

|            | Display Controller RGBA Background Color                                      |     |

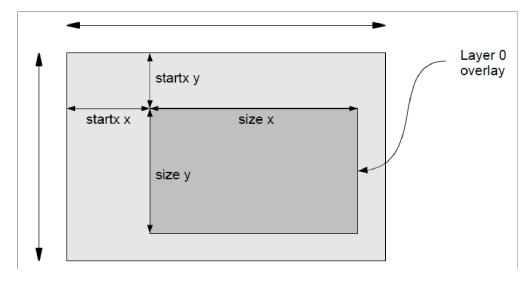

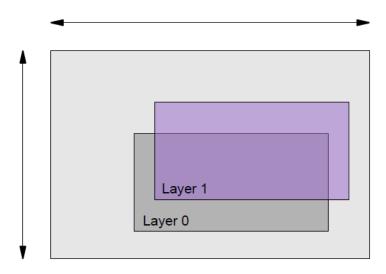

| Figure 84. | Display Controller First Layer                                                | 223 |

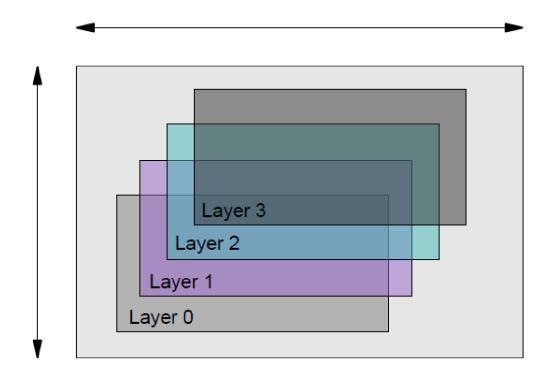

| Figure 85. | Display Controller Second Layer                                               | 224 |

| Figure 86. | Display Controller Third and Fourth Layers                                    | 225 |

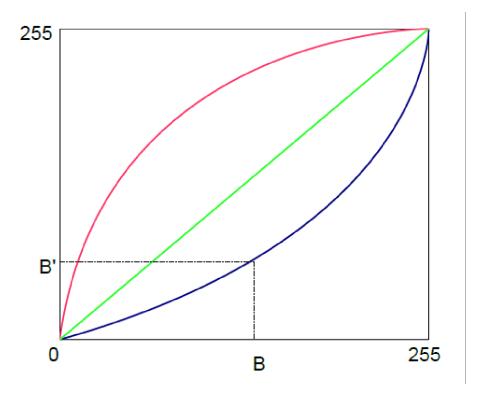

| Figure 87. | Gamma Correction of RGB Values                                                | 227 |

| Figure 88. | Dithering on Limited Color Palette                                            | 228 |

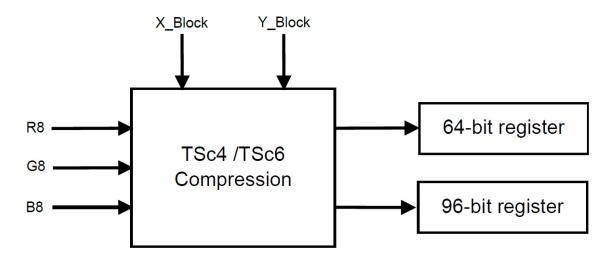

| Figure 89. | FTSC™4 /TSC™6 Framebuffer Compression Module                                  | 234 |

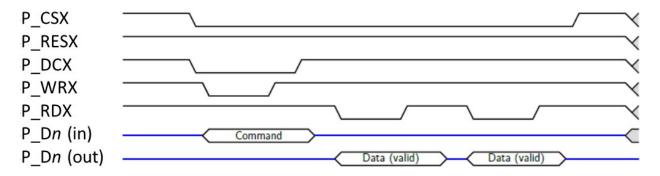

| Figure 90. | DBI-Type B Write Sequence                                                     | 235 |

| Figure 91. | DBI-Type B Read Sequence                                                      | 236 |

| Figure 92. | SPI 3- or 4-wire Interface (Dashed Line Used in 4-wire) - Data Out Only       | 241 |

| Figure 93. | SPI 3- or 4-wire Interface (Dashed Line Used in 4-wire) - Bi-directional Data | 241 |

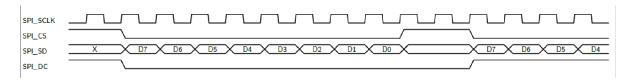

| Figure 94. | SPI 3-wire Serial Write Transmission                                          | 242 |

| Figure 95. | SPI 4-wire Serial Write Transmission                                          | 242 |

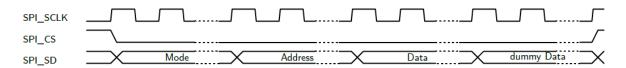

| Figure 96. | Single Line Update Mode                                                       | 242 |

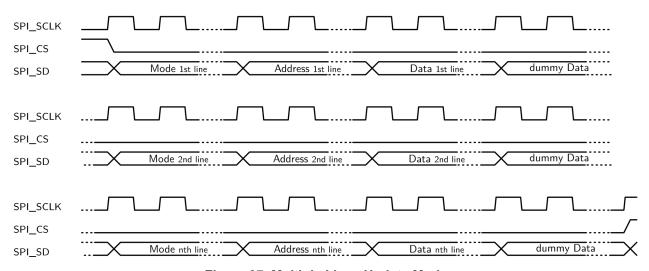

| Figure 97. | Multiple Lines Update Mode                                                    | 243 |

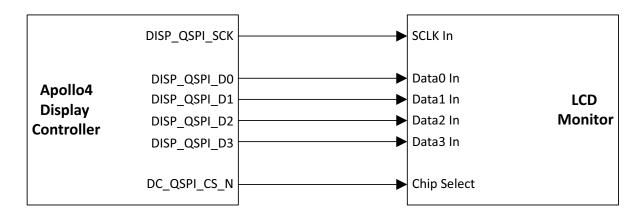

| Figure 98. | QuadSPI Interface                                                             | 246 |

| Figure 99. | DualSPI Interface                                                             | 247 |

|            | ). Rendering Flow                                                             |     |

|            | . GFX Library Architecture                                                    |     |

|            | P. GPU VLIW fragment instruction format                                       |     |

|            | 3. TSC™4 /TSC™6 Framebuffer Compression Module                                |     |

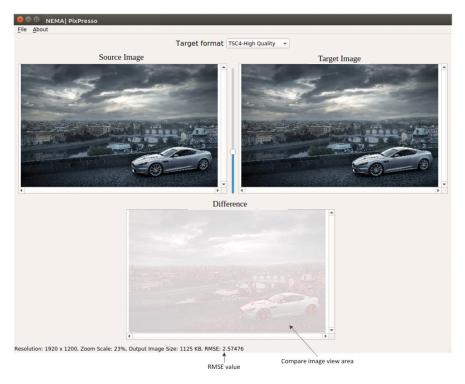

|            | I. NEMA®  PIX-Presso State after a Conversion                                 |     |

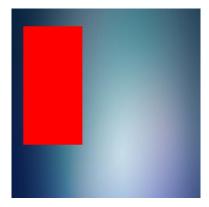

| -          | 5. Original Empty Framebuffer                                                 |     |

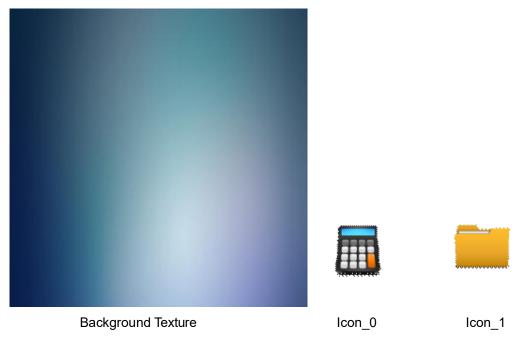

| Figure 106 | S. Image Background                                                           | 272 |

| Figure | 107. | Final Output of the Drawing Process        | 272 |

|--------|------|--------------------------------------------|-----|

| Figure | 108. | Rendered Scene with Two Icons              | 274 |

| Figure | 109. | Scene Textures                             | 275 |

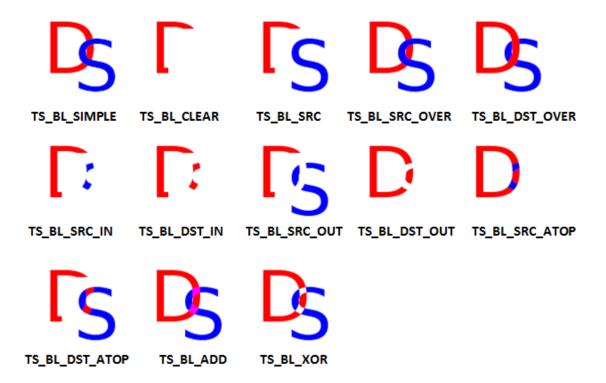

| Figure | 110. | Predefined Blending Modes                  | 280 |

| Figure | 111. | Original Framebuffer before Blending       | 280 |

| Figure | 112. | Scene Textures                             | 281 |

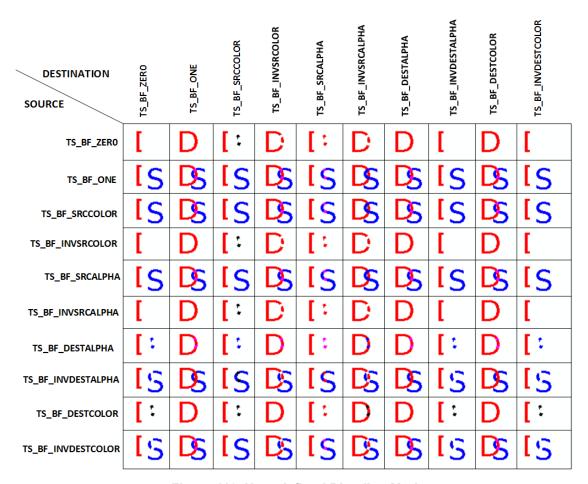

| Figure | 113. | User-defined Blending Modes                | 282 |

| Figure | 114. | Source Textures                            | 284 |

| Figure | 115. | Additional Operations Example              | 284 |

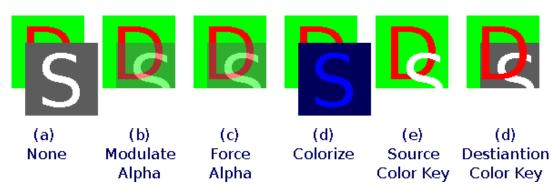

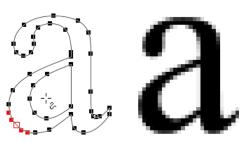

| Figure | 116. | Vector and Bitmap Fonts                    | 285 |

| Figure | 117. | Scan Flowchart                             | 374 |

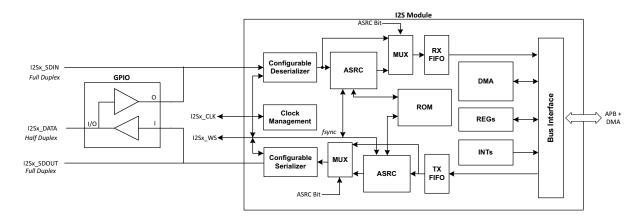

| Figure | 118. | I2S Block Diagram                          | 378 |

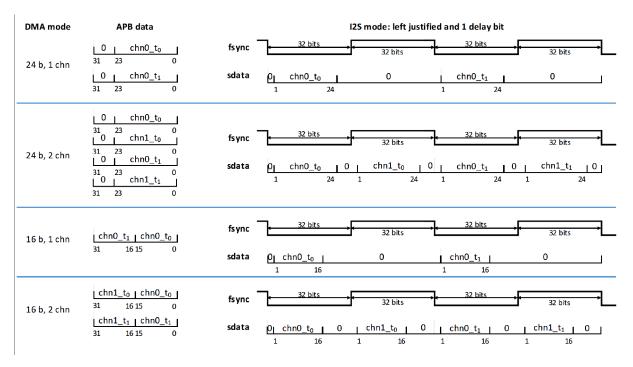

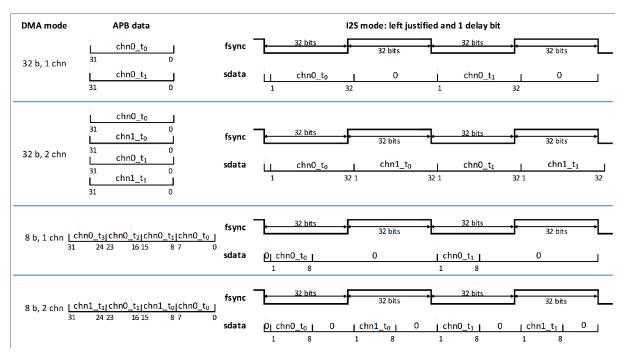

| Figure | 119. | DMA Configurations for 16 Bits and 24 Bits | 381 |

| Figure | 120. | DMA Configurations for 8 Bits and 32 Bits  | 381 |

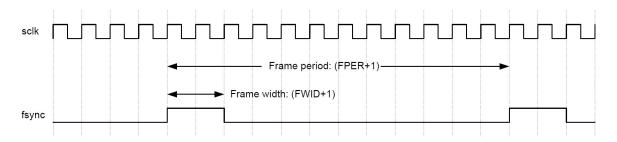

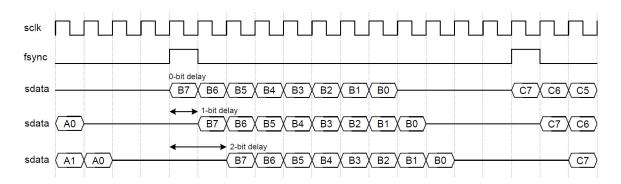

| Figure | 121. | Programmable Frame Period and Width        | 384 |

| Figure | 122. | Data Delay                                 | 384 |

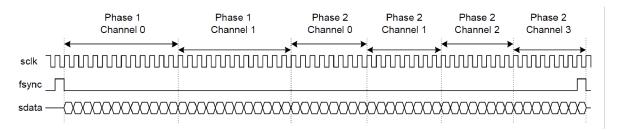

| Figure | 123. | Dual-phase Frame Example                   | 385 |

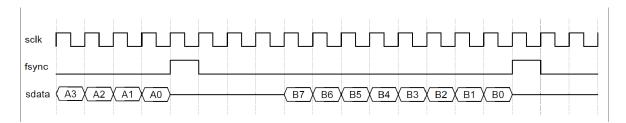

| Figure | 124. | Right Justification                        | 385 |

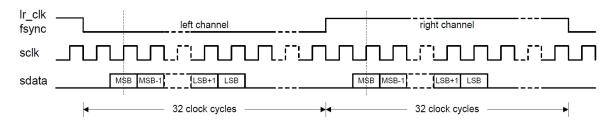

| Figure | 125. | I2S Formatted Audio Frame                  | 386 |

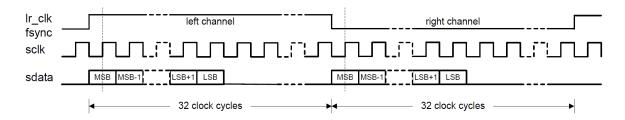

| Figure | 126. | Left-justified Audio Frame                 | 386 |

| Figure | 127. | Right-justified Audio Frame                | 387 |

# **List of Tables**

| Table 1: Document Revision History                              | 13 |

|-----------------------------------------------------------------|----|

| Table 2: ARM Cortex-M4 Vector Table for the Apollo4 Family      |    |

| Table 3: SoC Interrupt Assignments                              |    |

| Table 4: High-level Apollo4 / Apollo4 Blue Memory Map           | 20 |

| Table 5: High-level Apollo4 Plus / Apollo4 Blue Plus Memory Map | 20 |

| Table 6: Detailed Apollo4 / Apollo4 Blue Memory Map             | 21 |

| Table 7: Detailed Apollo4 Plus / Apollo4 Blue Plus Memory Map   |    |

| Table 8: SoC Peripheral Device Memory Map                       |    |

| Table 9: CPU Power Mode Transitions                             |    |

| Table 10: Clock Usage Table                                     |    |

| Table 11: Alarm RPT Function                                    |    |

| Table 12: Timer Modes                                           |    |

| Table 13: Interrupt Trigger Options                             |    |

| Table 14: IO Master 0 I2C Configuration                         |    |

| Table 15: IO Master 0 4-wire SPI Configuration                  |    |

| Table 16: IO Master 0 3-wire SPI Configuration                  |    |

| Table 17: IO Slave I2C Configuration                            |    |

| Table 18: IO Slave 4-wire SPI Configuration                     |    |

| Table 19: IO Slave 3-wire SPI Configuration                     |    |

| Table 19: 10 Slave 3-wire SFT Configuration                     |    |

| Table 21: UART0 TX Configuration                                |    |

| Table 22: UART0 TX Configuration                                |    |

|                                                                 |    |

| Table 23: UART0 RTS Configuration                               |    |

|                                                                 |    |

| Table 25: UART1 TX Configuration                                |    |

| Table 27: UART1 RTS Configuration                               |    |

| Table 28: UART1 CTS Configuration                               |    |

| Table 26: UART1 RX Configuration                                |    |

| Table 29: UART2 TX Configuration                                |    |

| Table 30: UART2 RX Configuration                                |    |

| Table 31: UART2 RTS Configuration                               |    |

| Table 32: UART2 CTS Configuration                               |    |

| Table 33: UART3 TX Configuration                                |    |

| Table 34: UART3 RX Configuration                                |    |

| Table 35: UART3 RTS Configuration                               |    |

| Table 37: PDM CLK Configuration                                 |    |

| Table 38: PDM DATA Configuration                                |    |

| Table 36: UART3 CTS Configuration                               |    |

| Table 39: I2S CLK Configuration                                 |    |

| Table 40: I2S WS Configuration                                  |    |

| Table 41: I2S DATA Configuration                                |    |

| Table 42: I2S SDIN Configuration                                |    |

| Table 43: I2S SDOUT Configuration                               |    |

| Table 44: SDIO/SDIF Configuration                               |    |

| Table 45: CLKOUT Configuration                                  |    |

| Table 46: 32 kHz CLKOUT Configuration                           |    |

| Table 47: CLKOUT_32M Configuration                              |    |

| Table 48: ADC Analog Input Configuration                        |    |

| Table 49: ADC Trigger Input Configuration                       |    |

| Table 50: Voltage Comparator Reference Configuration            |    |

| Table 51: Voltage Comparator Input Configuration                |    |

| Table 52: Voltage Comparator Output Configuration               | 79 |

| Table 53: SWO Configuration                                                             |     |

|-----------------------------------------------------------------------------------------|-----|

| Table 54: SW Trace Configuration                                                        |     |

| Table 55: One SLOT Configuration Register                                               | 85  |

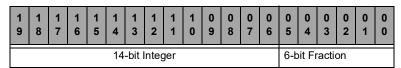

| Table 56: 14.6 GPADC Sample Format                                                      | 86  |

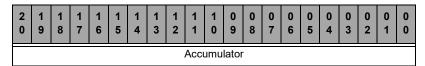

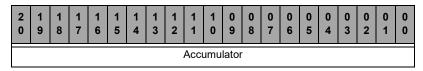

| Table 57: Per Slot Sample Accumulator                                                   | 86  |

| Table 58: Accumulator Scaling                                                           | 86  |

| Table 59: Accumulator Scaling                                                           | 86  |

| Table 60: FIFO Register                                                                 | 87  |

| Table 61: 12-bit FIFO Data Format                                                       | 87  |

| Table 62: 10-bit FIFO Data Format                                                       | 88  |

| Table 63: 8-bit FIFO Data Format                                                        | 88  |

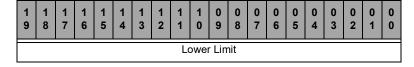

| Table 64: Window Comparator Lower Limit Register                                        | 89  |

| Table 65: Window Comparator Upper Limit Register                                        |     |

| Table 66: GPADC Power Modes                                                             |     |

| Table 67: Command Queue Example                                                         |     |

| Table 68: CQFLAGS                                                                       |     |

| Table 69: Registers/Fields Changed from Apollo4 to Apollo4 Plus                         |     |

| Table 70: Mapping of Direct Area Access Interrupts and Corresponding REGACCINTSTAT Bits |     |

| Table 71: I/O Interface Interrupt Control                                               |     |

| Table 72: HOST IER Register                                                             |     |

| Table 73: HOST_IER Register Bits                                                        | 141 |

| Table 74: HOST ISR Register                                                             | 142 |

| Table 75: HOST ISR Register Bits                                                        | 142 |

| Table 76: HOST_WCR Register                                                             | 142 |

| Table 77: HOST WCR Register Bits                                                        | 143 |

| Table 78: HOST_WCS Register                                                             | 143 |

| Table 79: HOST_WCS Register Bits                                                        | 143 |

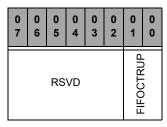

| Table 80: FIFOCTRLO Register                                                            | 144 |

| Table 81: FIFOCTRLO Register Bits                                                       | 144 |

| Table 82: FIFOCTRUP Register                                                            | 144 |

| Table 83: FIFOCTRUP Register Bits                                                       | 144 |

| Table 84: FIFO Register                                                                 | 145 |

| Table 85: FIFO Register Bits                                                            | 145 |

| Table 86: Index 0 (IDX0) Register Multi-function Fields                                 | 150 |

| Table 87: USB Controller Register Map Additions for Dynamic FIFO Sizing                 | 155 |

| Table 88: Unloaded Packet Sizes < MAXPAYLOAD Requiring Manual Clear of OutPktRdy        | 171 |

| Table 89: PID Errors and IncompRx Responses in Peripheral Mode                          | 174 |

| Table 90: IDX0 Register Field Settings for Bulk IN Endpoint                             | 176 |

| Table 91: IDX0 Register Field Settings for Bulk OUT Endpoint                            |     |

| Table 92: IDX0 Register Field Settings for Isochronous IN Endpoint                      | 181 |

| Table 93: IDX0 Register Field Settings for Isochronous OUT Endpoint                     |     |

| Table 94: PID Error or IncompRx Reporting in Peripheral Mode                            |     |

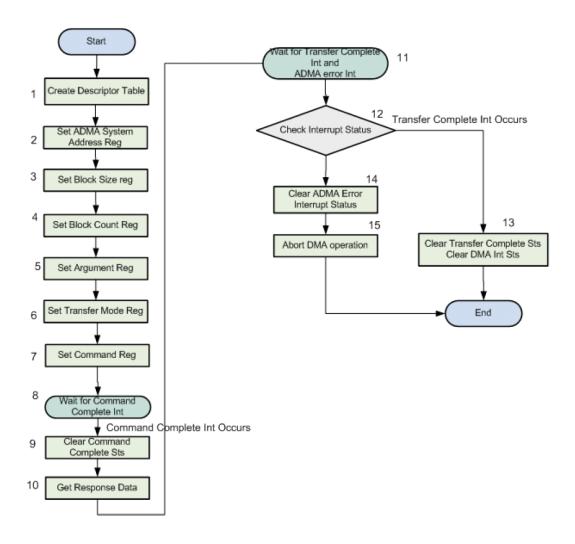

| Table 95: Non-DMA Transfer Flow Sequence Steps                                          |     |

| Table 96: DMA Transfer Flow Sequence Steps                                              | 211 |

| Table 97: ADMA Transaction Flow Sequence Steps                                          | 214 |

| Table 98: Layer 0 Example                                                               | 224 |

| Table 99: Blending Modes                                                                |     |

| Table 100: DestA Operand                                                                |     |

| Table 101: SUBOP0-Instructions                                                          |     |

| Table 102: A0 Operand                                                                   |     |

| Table 103: A1 Operand                                                                   |     |

| Table 104: A2 Operand                                                                   | 256 |

| Table 105: SUBOP1 Instructions                                                          |     |

| Table 106: DestRGB Operand                                                              | 257 |

| Table 107: RGB0 Operand                                                 | 258 |

|-------------------------------------------------------------------------|-----|

| Table 108: RGB1 Operand                                                 | 258 |

| Table 109: RGB2 Operand                                                 | 259 |

| Table 110: SUBOP2 Instructions                                          | 259 |

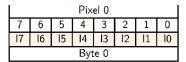

| Table 111: Pixel Operand                                                | 260 |

| Table 112: Addressing Coords Operand                                    | 260 |

| Table 113: TEXnBASE Coords Operand                                      | 260 |

| Table 114: SUBOP3 Instructions                                          |     |

| Table 115: LHS, RHS Operands                                            |     |

| Table 116: Supported formats                                            | 274 |

| Table 117: Shader conventions                                           | 274 |

| Table 118: Predefined Blending Modes                                    | 279 |

| Table 119: Blend Factors                                                | 282 |

| Table 120: ops Arguments                                                |     |

| Table 121: PDMA_CKO and OSR Settings for Different Sampling Frequencies | 360 |

| Table 122: PDM-to-PCM Converter Operating Mode                          |     |

| Table 123: 24-bit Unpacked Data                                         |     |

| Table 124: 16-bit Unpacked Data                                         |     |

| Table 125: 16-bit Packed Data                                           |     |

| Table 126: 8-bit Packed Data - Single Channel                           | 363 |

| Table 127: 8-bit Packed Data - Dual Channels                            | 364 |

| Table 128: 8-bit Packed Data - 8 Channels                               | 364 |

| Table 129: PGA Gain Control                                             | 365 |

| Table 130: SOFTMUTE Register Configuration                              |     |

| Table 131: LPF Parameters                                               |     |

| Table 132: 14.6 Audio ADC Sample Format                                 | 368 |

| Table 133: Per Slot Sample Accumulator                                  |     |

| Table 134: Accumulator Scaling                                          | 369 |

| Table 135: FIFO Register                                                | 369 |

| Table 136: 12-bit FIFO Data Format                                      | 369 |

| Table 137: 10-bit FIFO Data Format                                      | 370 |

| Table 138: 8-bit FIFO Data Format                                       |     |

| Table 139: Window Comparator Lower Limit Register                       |     |

| Table 140: Window Comparator Upper Limit Register                       |     |

| Table 141: Audio ADC Power Modes                                        |     |

| Table 142: Configurations Supported by the I2S Module                   |     |

| Table 143: Apollo4 SoC Ordering Information                             | 388 |

| Table 144: Apollo4 Plus SoC Ordering Information                        | 388 |

# 1. Introduction

The purpose of this Programmer's Guide is to provide developers using an Apollo4 family SoC with additional information to that found in the datasheets, specifically as it relates to programming the device for intended operation. The current SoCs that make up the Apollo4 family include the following:

- Apollo4

- Apollo4 Blue

- Apollo4 Plus

- Apollo4 Blue Plus

The Programmer's Guide and the relevant datasheet(s) are intended to supplement each other and the user should have ready access to one when referencing the other. This Programmer's Guide also refers to the AmbiqSuite SDK extensively, as the SDK is the programmers' primary source of software to use and control Apollo4 operation properly.

Unless stated otherwise, references in this guide to "Apollo4 SoC" pertain to all members of the Apollo4 family.

# 2. Document Revision History

**Table 1: Document Revision History**

| Revision | Date     | Description                                                                                                                                                                                                                                                                                                                                                                          |

|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | Apr 2020 | Document initial release                                                                                                                                                                                                                                                                                                                                                             |

| 2.0      | Apr 2020 | Added chapters: WDT, UART, DC, BLE Controller (appendix) Updated chapters: - GPIO: Updated Pin Muxing Table (CSP package pins) - PDM: Added "Supported Data Formats" section                                                                                                                                                                                                         |

| 3.0      | Jul 2020 | Initial version for silicon revision B Added chapters: USB Updated chapters: - GPIO: Pin Mapping, Pad Function Color Code, and Special Pad Types tables updated DC: Corrected pin names in "Serial Formats" section BLE Controller Appendix: Minor edits to transaction diagrams for clarity.                                                                                        |

| 3.1      | Oct 2020 | <ul> <li>CLKGEN: Removed digital calibration procedures for XT/LFRC and auto-calibration of LFRC, which have been deprecated.</li> <li>RTC: Removed references to deprecated features (12-hour clock mode, read error status (CKERR).</li> <li>GPIO: Removed unavailable external clocks in Pin Mapping Tables.</li> <li>DC: Display Formats content added from datasheet</li> </ul> |

| 4.0      | Oct 2020 | - I2C/SPI Slave Module: Direct Area Functions section updated to include Address Pointer Wrap Mode.                                                                                                                                                                                                                                                                                  |

| 4.1      | Dec 2020 | - CLKGEN: HFRC Auto-adjustment section updated TIMER: References to deprecated CONTINUOUS mode removed GPIO: Added replicated I2S0/I2S1 functions for sharing I2S ports on different devices in Rev B Pin Mapping Table. IO Master 0 4-wire SPI Connection section updated IOM: SPI Configuration section updated.                                                                   |

| 5.0      | Jun 2021 | - SoC Architecture: "DAXI Considerations" section added CLKGEN: "Clock Enablement for Modules with a Special Mux" section added TIMER: Updated modes of operation IOSLAVE: Added detail in "Wakeup Using the I2C/SPI Slave" section.                                                                                                                                                 |

| 6.0      | Sep 2021 | - SoC Architecture: Removed unsupported entries in "ARM Cortex-M4 Vector Table for Apollo4 SoC" and "SoC Interrupt Assignments" - TIMER: Removed references to STIMER selection as a timer's trigger.                                                                                                                                                                                |

**Table 1: Document Revision History**

| Revision | Date     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.0      | Oct 2022 | All: Apollo4 and Apollo4 Plus Programmer's Guides have been consolidated to include information/support for Apollo4 derivatives Apollo4, Apollo4 Blue, Apollo4 Plus, Apollo4 Blue Plus.  SoC Architecture: Added note about mode transitioning requirements described in ERR076. Updated "ARM Cortex-M4 Vector Table for Apollo4 SoC" to remove Secure Fault ISR and exception numbers above 99. Updated "DAXI Buffers and Flush/Invalidate Operations" section.  TIMER: Updated Edge mode operation in the "Timer Modes" table. Corrected pattern lengths of SINGLEPATTERN and REPEATPATTERN. Corrected "Terminating a Repeat Operation" section".  GPIO: Added note specifying that the DPI-2 interface is not supported. "Module-specific Pad Configuration" section updated to cover all Apollo4 devices.  GPADC: Updated "Clock Source and Divider" section and specified that only 24 MHz ADC clock is supported and noted that a minimum of 37 sampling/tracking cycles should be used. Added note specifying that a delay is required after CNVCMP ISR is asserted and before reading the FIFO.  MSPI: Added section "Clocking and Other Limitations" On Apollo4 / Apollo4 Blue the maximum clock rate for MSPI2 for quad and octal data widths has been updated to 24MHz SDR and 12MHz DDR. Added note specifying limitations for High Speed mode.  SDIO: Added note specifying limitations for High Speed mode.  SDIO: Added note specifying limitations for High Speed mode.  SDIO: Added. Uspala Controller: "Video Timing Generator" section renamed and updated.  12S: Added. UART: Clock selection updated to include 48 MHz. |

# 3. SoC Architecture

# 3.1 Interrupts

Within the SoC, multiple peripherals can generate interrupts. In some cases, a single peripheral may be able to generate multiple different interrupts. Each interrupt signal generated by a peripheral is connected back to the M4 core in two places. First, the interrupts are connected to the Nested Vectored Interrupt Controller, NVIC, in the core. This connection provides the standard changes to program flow associated with interrupt processing. Additionally, they are connected to the WIC outside of the core, allowing the interrupt sources to wake the M4 core when it is in a deep sleep (SRPG) mode.

The SoC supports the M4 NMI as well as the normal interrupt types. For details on the Interrupt model of the M4, please see the "Cortex-M4 Devices Generic User Guide," document number DUI0553A.

Below is the M4 Vector Table for the Apollo4 family. Note that not all modules listed in the table are on all family derivatives.

Table 2: ARM Cortex-M4 Vector Table for the Apollo4 Family

| Exception Number | IRQ   | Offset      | Vector      | Description      |

|------------------|-------|-------------|-------------|------------------|

| 99               | 83    | 0x18C       | IRQ83       | CPU (cache/DAXI) |

| 98               | 82    | 0x168       | IRQ82       | Timer 15         |

| 97               | 81    | 0x184       | IRQ81       | Timer 14         |

| 96               | 80    | 0x180       | IRQ80       | Timer 13         |

| 95               | 79    | 0x17C       | IRQ79       | Timer 12         |

| 94               | 78    | 0x178       | IRQ78       | Timer 11         |

| 93               | 77    | 0x174       | IRQ77       | Timer 10         |

| 92               | 76    | 0x170       | IRQ76       | Timer 9          |

| 91               | 75    | 0x16C       | IRQ75       | Timer 8          |

| 90               | 74    | 0x168       | IRQ74       | Timer 7          |

| 89               | 73    | 0x164       | IRQ73       | Timer 6          |

| 88               | 72    | 0x160       | IRQ72       | Timer 5          |

| 87               | 71    | 0x15C       | IRQ71       | Timer 4          |

| 86               | 70    | 0x158       | IRQ70       | Timer 3          |

| 85               | 69    | 0x154       | IRQ69       | Timer 2          |

| 84               | 68    | 0x150       | IRQ68       | Timer 1          |

| 83               | 67    | 0x14C       | IRQ67       | Timer 0          |

| 82               | 66    | 0x148       | IRQ66       | Reserved         |

| 81               | 65    | 0x144       | IRQ65       | Reserved         |

| 80               | 64    | 0x140       | IRQ64       | Reserved         |

| 72-79            | 56-63 | 0x120-0x13C | IRQ56-IRQ63 | GPIO             |

| 71               | 55    | 0x11C       | IRQ55       | Reserved         |

| 70               | 54    | 0x118       | IRQ54       | Reserved         |

| 69               | 53    | 0x114       | IRQ53       | Reserved         |

| 68               | 52    | 0x110       | IRQ52       | Reserved         |

| 67               | 51    | 0x10C       | IRQ51       | PDM3             |

| 66               | 50    | 0x108       | IRQ50       | PDM2             |

Table 2: ARM Cortex-M4 Vector Table for the Apollo4 Family

| Exception Number | IRQ   | Offset    | Vector      | Description                                    |

|------------------|-------|-----------|-------------|------------------------------------------------|

| 65               | 49    | 0x104     | IRQ49       | PDM1                                           |

| 64               | 48    | 0x100     | IRQ48       | PDM0                                           |

| 63               | 47    | 0xFC      | IRQ47       | Reserved                                       |

| 62               | 46    | 0xF8      | IRQ46       | Reserved                                       |

| 61               | 45    | 0xF4      | IRQ45       | 12S1                                           |

| 60               | 44    | 0xF0      | IRQ44       | 12S0                                           |

| 59               | 43    | 0xEC      | IRQ43       | Reserved                                       |

| 58               | 42    | 0xE8      | IRQ42       | LP-ADC                                         |

| 57               | 41    | 0xE4      | IRQ41       | Reserved                                       |

| 56               | 40    | 0xE0      | IRQ40       | Stimer Capture/Overflow                        |

| 48-55            | 32-39 | 0xC0-0xDC | IRQ32-IRQ39 | Stimer Compare[0:7]                            |

| 47               | 31    | 0xBC      | IRQ31       | Reserved                                       |

| 46               | 30    | 0xB8      | IRQ30       | DSI                                            |

| 45               | 29    | 0xB4      | IRQ29       | Display                                        |

| 44               | 28    | 0xB0      | IRQ28       | Graphics                                       |

| 43               | 27    | 0xAC      | IRQ27       | USB                                            |

| 42               | 26    | 0xA8      | IRQ26       | SDIO                                           |

| 41               | 25    | 0xA4      | IRQ25       | Reserved                                       |

| 40               | 24    | 0xA0      | IRQ24       | CRYPTO Secure                                  |

| 39               | 23    | 0x9C      | IRQ23       | Clock Control                                  |

| 38               | 22    | 0x98      | IRQ22       | MSPI2                                          |

| 37               | 21    | 0x94      | IRQ21       | MSPI1                                          |

| 36               | 20    | 0x90      | IRQ20       | MSPI0                                          |

| 35               | 19    | 0x8C      | IRQ19       | GP-ADC                                         |

| 34               | 18    | 0x88      | IRQ18       | UART3                                          |

| 33               | 17    | 0x84      | 1RQ17       | UART2                                          |

| 32               | 16    | 0x80      | IRQ16       | UART1                                          |

| 31               | 15    | 0x7C      | IRQ15       | UART0                                          |

| 30               | 14    | 0x78      | IRQ14       | Counter/Timers (combined - also see IRQ 67-82) |

| 29               | 13    | 0x74      | IRQ13       | I2C/SPI Master7                                |

| 28               | 12    | 0x70      | IRQ12       | I2C/SPI Master6                                |

| 27               | 11    | 0x6C      | IRQ11       | I2C/SPI Master5                                |

| 26               | 10    | 0x68      | IRQ10       | I2C/SPI Master4                                |

| 25               | 9     | 0x64      | IRQ9        | I2C/SPI Master3                                |

| 24               | 8     | 0x60      | IRQ8        | I2C/SPI Master2                                |

| 23               | 7     | 0x5C      | IRQ7        | I2C/SPI Master1                                |

| 22               | 6     | 0x58      | IRQ6        | I2C/SPI Master0                                |

| 21               | 5     | 0x54      | IRQ5        | I2C/SPI Slave Register Access                  |

| 20               | 4     | 0x50      | IRQ4        | I2C/SPI Slave                                  |

| 19               | 3     | 0x4C      | IRQ3        | Voltage Comparator                             |

Table 2: ARM Cortex-M4 Vector Table for the Apollo4 Family

| Exception Number | IRQ | Offset | Vector         | Description             |

|------------------|-----|--------|----------------|-------------------------|

| 18               | 2   | 0x48   | IRQ2           | RTC                     |

| 17               | 1   | 0x44   | IRQ1           | Watchdog Timer          |

| 16               | 0   | 0x40   | IRQ0           | Brownout Detection      |

| 15               | -1  | 0x3C   | Systick_S      |                         |

| 14               | -2  | 0x38   | PendSV_S       |                         |

| 13               | -   | 0x34   | Reserved       |                         |

| 12               | -4  | 0x30   | DebugMonitor   |                         |

| 11               | -5  | 0x2C   | SVCall_S       |                         |

| 10               | -   | 0x28   |                |                         |

| 9                | -   | 0x24   | Reserved       |                         |

| 8                | -   | 0x20   | Reserved       |                         |

| 7                | -   | 0x1C   |                |                         |

| 6                | -10 | 0x18   | UsageFault_S   | Usage Fault             |

| 5                | -11 | 0x14   | BusFault_S     | Bus Fault               |

| 4                | -12 | 0x10   | MemoryManage_S | Memory Management Fault |

| 3                | -13 | 0xC    | HardFault_S    | Hard Fault              |

| 2                | -14 | 0x8    | NMI_S          | Unused                  |

| 1                | -   | 0x4    | Reset          |                         |

|                  |     | 0x0    | Initial SP     |                         |

## **NOTE**

MSPI1 is not available on the Apollo4 Blue SoC or on the KBR package of the Apollo4 Blue Plus SoC.

Hardware interrupts are assigned in the SoC to the M4 NVIC as shown below.

**Table 3: SoC Interrupt Assignments**

| IRQ         | Peripheral/Description                       |  |

|-------------|----------------------------------------------|--|

| NMI         | Unused                                       |  |

| IRQ0        | Brownout Detection                           |  |

| IRQ1        | Watchdog Timer                               |  |

| IRQ2        | RTC                                          |  |

| IRQ3        | Voltage Comparator                           |  |

| IRQ4        | I <sup>2</sup> C / SPI Slave                 |  |

| IRQ5        | I <sup>2</sup> C / SPI Slave Register Access |  |

| IRQ6-IRQ13  | I <sup>2</sup> C / SPI Master0-7             |  |

| IRQ14       | Counter/Timers                               |  |

| IRQ15-IRQ18 | UART0-UART3                                  |  |

| IRQ19       | GP-ADC                                       |  |

| IRQ20-IRQ22 | MSPI0-MSPI2                                  |  |

| IRQ23       | Clock Control                                |  |

| IRQ24       | CRYPTO Secure                                |  |

| IRQ25       | Reserved                                     |  |

| IRQ26       | SDIO                                         |  |

| IRQ27       | USB                                          |  |

| IRQ28       | Graphics                                     |  |

| IRQ29       | Display                                      |  |

| IRQ30       | DSI                                          |  |

| IRQ31       | Reserved                                     |  |

| IRQ32-IRQ39 | Stimer Compare[0:7]                          |  |

| IRQ40       | Stimer Capture/Overflow                      |  |

| IRQ41       | Reserved                                     |  |

| IRQ42       | LP-ADC                                       |  |

| IRQ43       | Reserved                                     |  |

| IRQ44-IRQ45 | 12S0-12S1                                    |  |

| IRQ46-IRQ47 | Reserved                                     |  |

| IRQ48-IRQ51 | PDM0-PDM3                                    |  |

**Table 3: SoC Interrupt Assignments**

| IRQ         | Peripheral/Description |

|-------------|------------------------|

| IRQ52       | Reserved               |

| IRQ53       | Reserved               |

| IRQ54       | Reserved               |

| IRQ55       | Reserved               |

| IRQ56-IRQ63 | GPIO                   |

| IRQ64       | Reserved               |

| IRQ65       | Reserved               |

| IRQ66       | Reserved               |

| IRQ67-IRQ82 | Timer0-Timer15         |

| IRQ83       | CPU (cache/DAXI)       |

All rights reserved.

#### **Memory Map** 3.2

The high-level SoC-specific memory map is as shown in the following tables.

Table 4: High-level Apollo4 / Apollo4 Blue Memory Map

| Address                 | Name            | Executable <sup>a</sup> | Description                                                         |

|-------------------------|-----------------|-------------------------|---------------------------------------------------------------------|

| 0x00000000 - 0x001FFFFF | MRAM            | Y                       | Internal Non-volatile MRAM memory                                   |

| 0x00200000 - 0x07FFFFFF | Reserved        | Х                       | No device at this address range                                     |

| 0x08000000 - 0x08000FFF | Boot Loader ROM | Y                       | Execute Only Boot Loader and MRAM Helper Functions.                 |

| 0x08001000 – 0x0FFFFFF  | Reserved        | Х                       | No device at this address range                                     |

| 0x10000000 - 0x101D7FFF | SRAM            | Y/N                     | SRAM Memory (execution depends on which memory is being referenced) |

| 0x101D8000 - 0x13FFFFF  | Reserved        | Х                       | Reserved                                                            |

| 0x14000000 – 0x1FFFFFF  | External NVM    | Y                       | External Memory                                                     |

| 0x20000000 – 0x3FFFFFF  | Reserved        | Х                       | Reserved                                                            |

| 0x40000000 – 0x4FFFFFF  | Peripheral      | N                       | Peripheral devices                                                  |

| 0x50000000 – 0xDFFFFFF  | Reserved        | Х                       | No device at this address range                                     |

| 0xE0000000 - 0xE00FFFF  | PPB             | N                       | NVIC, System timers, System Control Block                           |

| 0xE0100000 – 0xFFFFFFF  | Reserved        | Х                       | No device at this address range                                     |

a. "Y" = Yes, "N" = No, "X" = Does not apply

Table 5: High-level Apollo4 Plus / Apollo4 Blue Plus Memory Map

| Address                 | Name            | Executable <sup>a</sup> | Description                                                         |

|-------------------------|-----------------|-------------------------|---------------------------------------------------------------------|

| 0x00000000 - 0x001FFFFF | MRAM            | Y                       | Internal Non-volatile MRAM memory                                   |

| 0x00200000 - 0x07FFFFFF | Reserved        | Х                       | No device at this address range                                     |

| 0x08000000 - 0x08000FFF | Boot Loader ROM | Y                       | Execute Only Boot Loader and MRAM Helper Functions.                 |

| 0x08001000 – 0x0FFFFFF  | Reserved        | Х                       | No device at this address range                                     |

| 0x10000000 – 0x102BFFFF | SRAM            | Y/N                     | SRAM Memory (execution depends on which memory is being referenced) |

| 0x102C0000 - 0x13FFFFF  | Reserved        | Х                       | Reserved                                                            |

| 0x14000000 – 0x1FFFFFF  | External NVM    | Y                       | External Memory                                                     |

| 0x20000000 – 0x3FFFFFF  | Reserved        | Х                       | Reserved                                                            |

| 0x40000000 – 0x4FFFFFF  | Peripheral      | N                       | Peripheral devices                                                  |

| 0x50000000 – 0xDFFFFFF  | Reserved        | Х                       | No device at this address range                                     |

| 0xE0000000 - 0xE00FFFF  | PPB             | N                       | NVIC, System timers, System Control Block                           |

| 0xE0100000 – 0xFFFFFFF  | Reserved        | Х                       | No device at this address range                                     |

a. "Y" = Yes, "N" = No, "X" = Does not apply

A more detailed view of the device-specific memory map, which breaks out the various memory types and locations, is as shown in the following tables.

Table 6: Detailed Apollo4 / Apollo4 Blue Memory Map

| Address                 | Name            | Executable <sup>a</sup> | Cacheable <sup>a</sup> | Description                                         |

|-------------------------|-----------------|-------------------------|------------------------|-----------------------------------------------------|

| 0x00000000 - 0x001FFFFF | MRAM            | Y                       | I & D                  | Internal Non-volatile MRAM Memory                   |

| 0x00200000 - 0x07FFFFF  | Reserved        | Х                       | Х                      | No device at this address range                     |

| 0x08000000 – 0x08000FFF | Boot Loader ROM | Y                       | N                      | Execute Only Boot Loader and MRAM Helper Functions. |

| 0x08001000 - 0x0FFFFFF  | Reserved        | Х                       | Х                      | No device at this address range                     |

| 0x10000000 - 0x1005FFFF | CPU SRAM (TCM)  | Y                       | N                      | Low-power / Low Latency SRAM (TCM)                  |

| 0x10060000 - 0x1015FFFF | System SRAM     | Y                       | I only                 | Shared System SRAM (SSRAM)                          |

| 0x10160000 - 0x101D7FFF | Extended SRAM   | N                       | I only                 | Extended Memory                                     |

| 0x101D8000 - 0x13FFFFFF | Reserved        | Х                       | Х                      | Reserved                                            |

| 0x14000000 - 0x17FFFFF  | MSPI0           | N                       | I only                 | Memory Mapped MSPI 0 Aperture                       |

| 0x18000000 - 0x1BFFFFFF | MSPI1           | N                       | I only                 | Memory Mapped MSPI 1 Aperture                       |

| 0x1C000000 – 0x1FFFFFF  | MSPI2           | N                       | I only                 | Memory Mapped MSPI 2 Aperture                       |

| 0x20000000 – 0x3FFFFFF  | Reserved        | Х                       | Х                      | Reserved                                            |

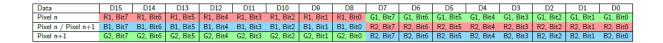

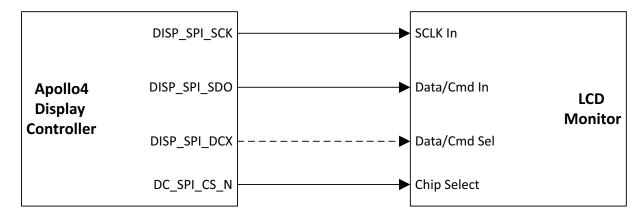

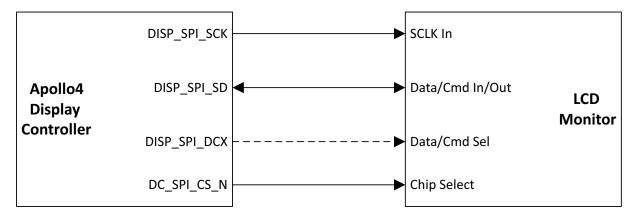

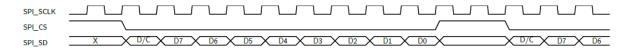

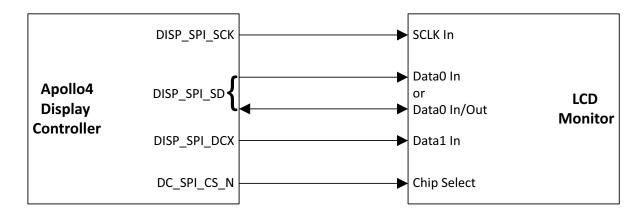

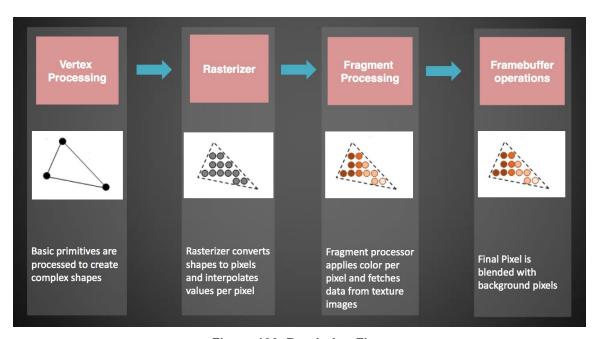

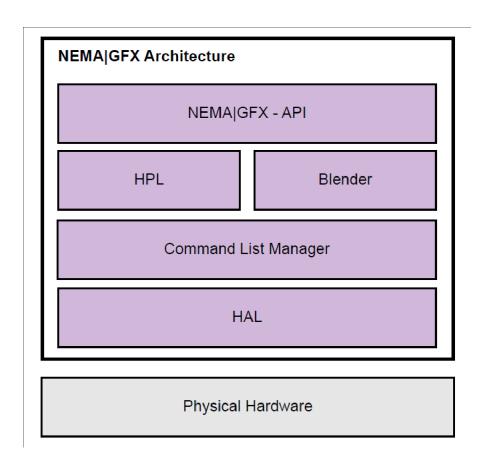

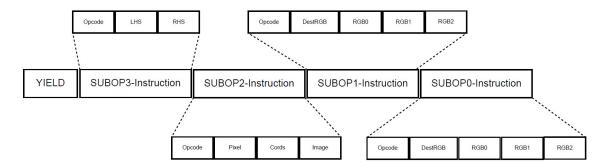

| 0x40000000 – 0x4FFFFFF  | Peripheral      | N                       | N                      | Peripheral devices                                  |